# **Brushless DC Motor Controller**

Check for Samples: UC1625, UC2625, UC3625

### **FEATURES**

- Drives Power MOSFETs or Power Darlingtons Directly

- 50-V Open Collector High-Side Drivers

- Latched Soft Start

- High-Speed Current-Sense Amplifier with Ideal Diode

- Pulse-by-Pulse and Average Current Sensing

- Over-Voltage and Under-Voltage Protection

- Direction Latch for Safe Direction Reversal

- Tachometer

- Trimmed Reference Sources 30 mA

- Programmable Cross-Conduction Protection

- Two-Quadrant and Four-Quadrant Operation

#### DESCRIPTION

The UC3625 family of motorcontroller devices integrate most of the functions required for high-performance brushless dc-motor control into one package. When coupled with external power MOSFETs or Darlingtons, these devices perform fixed-frequency PWM motor control in either voltage or current mode while implementing closed-loop speed control and braking with smart noise rejection, safe direction reversal, and cross—conduction protection.

Although specified for operation from power supplies between 10 V and 18 V, the UC1625 controls higher voltage power devices with external level-shifting components. The UC1625 contains fast, high-current push-pull drivers for low-side power devices and 50-V open-collector outputs for high-side power devices or level-shifting circuitry.

The UC1625 is characterized for operation over the military temperature range of -55°C to +125°C, while the UC2625 is characterized from -40°C to +105°C and the UC3625 is characterized from 0°C to +70°C. (**Note:** ESD Protection to 2 kV)

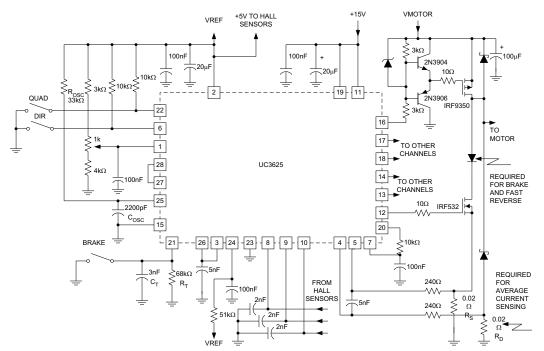

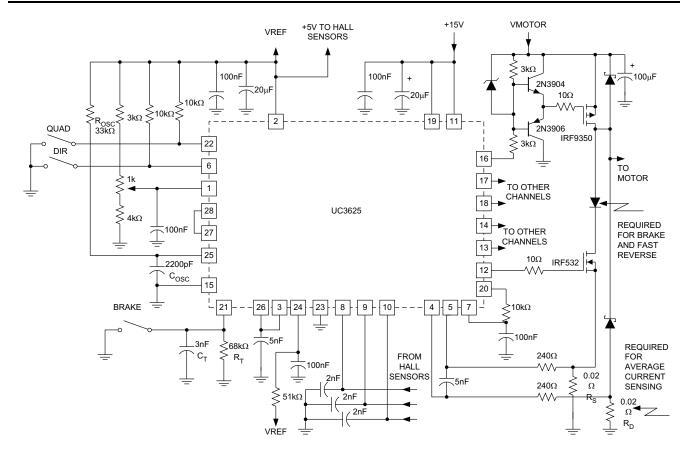

### TYPICAL APPLICATION

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

# ABSOLUTE MAXIMUM RATINGS(1)

over operating free-air temperature range (unless otherwise noted)

|                    |                                           | VALUE           | UNIT |  |  |  |  |  |

|--------------------|-------------------------------------------|-----------------|------|--|--|--|--|--|

| VCC                |                                           | 20              |      |  |  |  |  |  |

| Pwr<br>VCC         | Supply voltage                            | 20              |      |  |  |  |  |  |

|                    | PWM IN                                    | -0.3 to +6      |      |  |  |  |  |  |

|                    | E/A IN(+), E/A IN(-)                      | -0.3 to +12     | V    |  |  |  |  |  |

|                    | ISENSE1, ISENSE2                          | -1.3 to +6      |      |  |  |  |  |  |

|                    | OV-COAST, DIR, SPEED-IN, SSTART, QUAD SEL | -0.3 to +8      |      |  |  |  |  |  |

|                    | H1, H2, H3                                | -0.3 to +12     |      |  |  |  |  |  |

|                    | PU Output Voltage                         | -0.3 to +50     |      |  |  |  |  |  |

| PU                 |                                           | +200 continuous |      |  |  |  |  |  |

| PD                 |                                           | ±200 continuous |      |  |  |  |  |  |

| E/A                |                                           | ±10             |      |  |  |  |  |  |

| I <sub>SENSE</sub> | Output Current                            | -10             | mA   |  |  |  |  |  |

| Tach<br>Out        |                                           | ±10             |      |  |  |  |  |  |

| $V_{REF}$          |                                           | -50 continuous  |      |  |  |  |  |  |

|                    | Operating Temperature Range UC1625        | -55 to +125     |      |  |  |  |  |  |

| $T_J$              | Operating Temperature Range UC2625        | -40 to +105     | °C   |  |  |  |  |  |

|                    | Operating Temperature Range UC3625        | 0 to +70        |      |  |  |  |  |  |

| T <sub>stg</sub>   | Storage Temperature                       | -65 to +150     | °C   |  |  |  |  |  |

<sup>(1)</sup> Currents are positive into and negative out of the specified terminal.

Figure 1. CONNECTION DIAGRAM

A. This pinout applies to the SOIC (DW), PLCC (Q), and LCC (L) packages (for example: pin 22 has the same function on all packages.)

## **ELECTRICAL CHARACTERISTICS**

Unless otherwise stated, these specifications apply for:  $T_A = 25^{\circ}C$ ; Pwr  $V_{CC} = V_{CC} = 12$  V;  $R_{OSC} = 20$  k $\Omega$  to  $V_{REF}$ ;  $C_{OSC} = 2$  nF;  $R_{TACH} = 33$  k $\Omega$ ;  $C_{TACH} = 10$  nF; and all outputs unloaded.  $T_A = T_J$ .

|                    | PARAMETER                                                | TEST CONDITIONS                                                   | MIN  | TYP  | MAX  | UNIT |

|--------------------|----------------------------------------------------------|-------------------------------------------------------------------|------|------|------|------|

| Overall            |                                                          |                                                                   |      |      |      |      |

|                    | Supply current                                           |                                                                   |      | 14.5 | 30.0 | mA   |

|                    | VCC turn-on threshold                                    | Over operating range                                              | 8.65 | 8.95 | 9.45 |      |

|                    | VCC turn-off threshold                                   | o to reportating range                                            | 7.75 | 8.05 | 8.55 | V    |

| Overvolts          | age/Coast                                                |                                                                   | 7.70 | 0.00 | 0.00 |      |

| over voite         | OV-COAST inhibit threshold                               |                                                                   | 1.65 | 1.75 | 1.85 |      |

|                    | OV-COAST restart threshold                               |                                                                   | 1.55 | 1.65 | 1.75 | V    |

|                    |                                                          | Over operating range                                              |      |      |      | v    |

|                    | OV-COAST hysteresis                                      |                                                                   | 0.05 | 0.10 | 0.15 |      |

|                    | OV-COAST input current                                   |                                                                   | -10  | -1   | 0    | μA   |

| Logic Inp          |                                                          |                                                                   |      |      |      |      |

|                    | H1, H2, H3 low threshold                                 | Over operating range                                              | 8.0  | 1.0  | 1.2  | V    |

|                    | H1, H2, H3 high threshold                                |                                                                   | 1.6  | 1.9  | 2.0  |      |

|                    | H1, H2, H3 input current                                 | Over operating range, to 0 V                                      | -400 | -250 | -120 | μA   |

|                    | QUAD SEL, dir thresholds                                 | Over operating range                                              | 0.8  | 1.4  | 2.0  | V    |

|                    | QUAD SEL hysteresis                                      |                                                                   |      | 70   |      | mV   |

|                    | DIR hysteresis                                           |                                                                   |      | 0.6  |      | V    |

|                    | QUAD SEL input current                                   |                                                                   | -30  | 50   | 150  |      |

|                    | DIR input current                                        |                                                                   | -30  | -1   | 30   | μA   |

| PWM Am             | p/Comparator                                             |                                                                   |      |      |      |      |

|                    | E/A IN(+), E/A IN(-) input current                       | To 2.5 V                                                          | -5.0 | -0.1 | 5.0  |      |

|                    | PWM IN input current                                     | To 2.5 V                                                          | 0    | 3    | 30   | μA   |

|                    | Error amp input offset                                   | 0 V < V <sub>COMMON-MODE</sub> < 3 V                              | -10  |      | 10   | mV   |

|                    | Error amp voltage gain                                   |                                                                   | 70   | 90   |      | dB   |

|                    | E/A OUT range                                            |                                                                   | 0.25 |      | 3.50 | V    |

|                    | Pull-up current                                          | To 0 V                                                            | -16  | -10  | -5   | μA   |

| S <sub>START</sub> | Discharge current                                        | To 2.5 V                                                          | 0.1  | 0.4  | 3.0  | mA   |

| START              | Restart threshold                                        | 10 2.0 1                                                          | 0.1  | 0.2  | 0.3  | V    |

| Current A          |                                                          |                                                                   | 0    | 0.2  | 0.0  |      |

|                    | Gain                                                     | I <sub>SENSE1</sub> = 0.3 V, I <sub>SENSE2</sub> = 0.5 V to 0.7 V | 1.75 | 1.95 | 2.15 | V/V  |

|                    | Level shift                                              | I <sub>SENSE1</sub> = 0.3 V, I <sub>SENSE2</sub> = 0.3 V          | 2.4  | 2.5  | 2.65 |      |

|                    | Peak current threshold                                   |                                                                   | 0.14 | 0.20 | 0.26 | V    |

|                    | Over current threshold                                   | I <sub>SENSE1</sub> = 0 V, force I <sub>SENSE2</sub>              | 0.26 | 0.30 | 0.36 |      |

|                    | I <sub>SENSE1</sub> , I <sub>SENSE2</sub> input current  |                                                                   | -850 | -320 | 0    |      |

|                    | I <sub>SENSE1</sub> , I <sub>SENSE2</sub> offset current | To 0 V                                                            |      | ±2   | ±12  | μΑ   |

|                    | Range I <sub>SENSE1</sub> , I <sub>SENSE2</sub>          |                                                                   | -1   |      | 2    | V    |

| Tachome            | eter/Brake                                               |                                                                   | •    |      | -    | •    |

|                    | TACH-OUT high level                                      | Over energing record 40 kg to 0.5                                 | 4.7  | 5    | 5.3  |      |

|                    | TACH-OUT low level                                       | Over operating range, 10 kΩ to 2.5 V                              | 7.1  | 3    | 0.2  | V    |

|                    | On time                                                  | -                                                                 | 170  | 220  |      |      |

|                    |                                                          | Over energing reases                                              | 170  | 0.1% | 280  | μs   |

|                    | On time change with temp                                 | Over operating range                                              | 4.0  |      |      | A    |

|                    | RC-BRAKE input current                                   | To 0 V                                                            | -4.0 | -1.9 |      | mA   |

|                    | Threshold to brake, RC-brake                             | Over operating range                                              | 0.8  | 1.0  | 1.2  | V    |

|                    | Brake hysteresis, RC-brake                               |                                                                   |      | 0.09 |      |      |

|                    | SPEED-IN threshold                                       | Over operating range                                              | 220  | 257  | 290  | mV   |

|                    | SPEED-IN input current                                   |                                                                   | -30  | -5   | 30   | μΑ   |

# **ELECTRICAL CHARACTERISTICS (continued)**

Unless otherwise stated, these specifications apply for:  $T_A = 25^{\circ}C$ ; Pwr  $V_{CC} = V_{CC} = 12$  V;  $R_{OSC} = 20$  k $\Omega$  to  $V_{REF}$ ;  $C_{OSC} = 2$  nF;  $R_{TACH} = 33$  k $\Omega$ ;  $C_{TACH} = 10$  nF; and all outputs unloaded.  $T_A = T_J$ .

|         | PARAMETER                                | TEST CONDITIONS                  | MIN | TYP  | MAX | UNIT |  |

|---------|------------------------------------------|----------------------------------|-----|------|-----|------|--|

| Low-S   | ide Drivers                              |                                  | 1   |      |     |      |  |

|         | Voh, −1 mA, down from V <sub>CC</sub>    |                                  |     | 1.60 | 2.1 |      |  |

|         | V Voh, –50 mA, down from V <sub>CC</sub> | 0                                |     | 1.75 | 2.2 | V    |  |

|         | Vol, 1 mA                                | Over operating range             |     | 0.05 | 0.4 | V    |  |

|         | Vol, 50 mA                               |                                  |     | 0.36 | 0.8 |      |  |

|         | Rise/fall time                           | 10% to 90% slew time, into 1 nF  |     | 50   |     | ns   |  |

| High-S  | ide Drivers                              |                                  |     | ·    | ·   |      |  |

|         | Vol, 1 mA                                | Over energting range             |     | 0.1  | 0.4 | V    |  |

|         | Vol, 50 mA                               | Over operating range             |     | 1.0  | 1.8 | V    |  |

|         | Leakage current                          | Output voltage = 50 V            |     |      | 25  | μΑ   |  |

|         | Fall time                                | 10% to 90% slew time, 50 mA load |     | 50   |     | ns   |  |

| Oscilla | itor                                     |                                  |     |      |     |      |  |

|         | Fraguena                                 |                                  | 40  | 50   | 60  | kHz  |  |

|         | Frequency                                | Over operating range             | 35  |      | 65  | KΠZ  |  |

| Refere  | nce                                      | ·                                | ·   | ·    | ·   |      |  |

|         | Output valtage                           |                                  | 4.9 | 5.0  | 5.1 | V    |  |

|         | Output voltage                           | Over operating range             | 4.7 | 5.0  | 5.3 | V    |  |

|         | Load regulation                          | 0 mA to -20 mA load              | -40 | -5   |     | mV   |  |

|         | Line regulation                          | 10 V to 18 V V <sub>CC</sub>     | -10 | -1   | 10  | IIIV |  |

|         | Short circuit current                    | Over operating range             | 50  | 100  | 150 | mA   |  |

| Miscel  | laneous                                  |                                  |     |      |     |      |  |

|         | Output turn-on delay                     |                                  |     | 1    |     |      |  |

|         | Output turn-off delay                    |                                  |     | 1    |     | μs   |  |

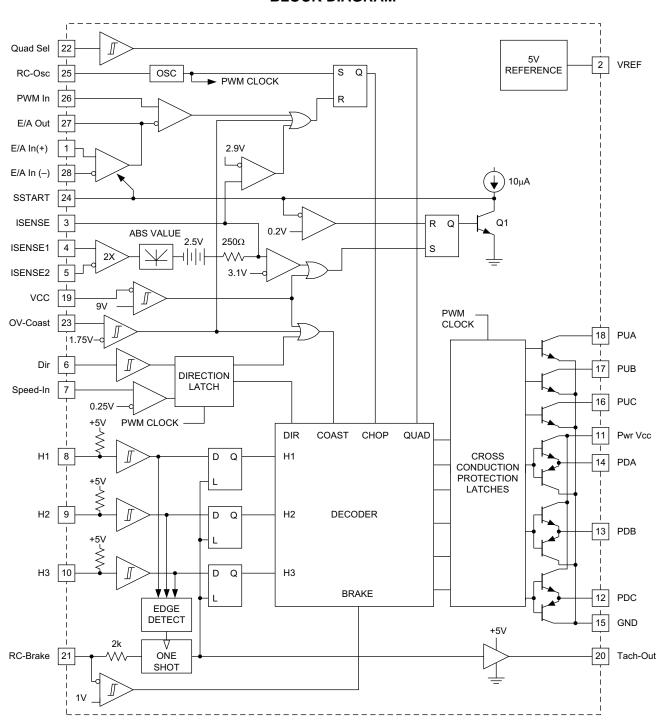

### **BLOCK DIAGRAM**

## **DEVICE INFORMATION**

## **Terminal Functions**

| TERMINAL                                 |                  | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------------------------------------|------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                                     | NO.              | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| DIR, SPEED-IN                            | 6, 7             |     | The position decoder logic translates the Hall signals and the DIR signal to the correct driver signals (PUs and PDs). To prevent output stage damage,the signal on DIR is first loaded into a direction latch, then shifted through a two-bit register. As long as SPEED-IN is less than 250 mV, the direction latch is transparent. When SPEED-IN is higher than 250 mV, the direction latch inhibits all changes indirection. SPEED-IN can be connected to TACH-OUT through a filter, so that the direction latch is only transparent when the motor is spinning slowly, and has too little stored energy to damage power devices.  Additional circuitry detects when the input and output of the direction latch are different, or when the input and output of the shift register are different, and inhibits all output drives during that time. This can be used to allow the motor to coast to a safe speed before reversing.  The shift register ensures that direction can not be changed instantaneously. The register is clocked by the PWM oscillator, so the delay between direction changes is always going to be between one and two oscillator periods. At 40 kHz, this corresponds to a delay of between 25 µs and 50 µs. Regardless of output stage, 25-µs deadtime should be adequate to ensure no overlap cross-conduction.  Toggling DIR causes an output pulse on TACH-OUT regardless of motor speed.              |

| E/A IN(+), E/A IN(-), E/A<br>OUT, PWM IN | 1, 28, 27,<br>26 |     | E/A IN(+) and E/A IN(-) are not internally committed to allow for a wide variety of uses. They can be connected to the ISENSE, to TACH-OUT through a filter, to an external command voltage, to a D/A converter for computer control, or to another op amp for more elegant feedback loops. The error amplifier is compensated for unity gain stability, so E/A OUT can be tied to E/A IN(-) for feedback and major loop compensation.  E/A OUT and PWM In drive the PWM comparator. For voltage-mode PWM systems, PWM In can be connected to RC-OSC. The PWM comparator clears the PWM latch, commanding the outputs to chop.  The error amplifier can be biased off by connecting E/A IN(-) to a higher voltage than /EA IN(+). When biased off, E/A OUT appears to the application as a resistor to ground. E/A OUT can then be driven by an external amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| GND                                      | 15               |     | All thresholds and outputs are referred to the GND pin except for the PD and PU outputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| H1, H2, H3                               | 8, 9, 10         |     | The three shaft position sensor inputs consist of hysteresis comparators with input pull-up resistors. Logic thresholds meet TTL specifications and can be driven by 5-V CMOS, 12-V CMOS, NMOS, or open-collectors. Connect these inputs to motor shaft position sensors that are positioned 120 electrical degrees apart. If noisy signals are expected, zener clamp and filter these inputs with 6-V zeners and an RC filter. Suggested filtering components are 1 k $\Omega$ and 2 nF. Edge skew in the filter is not a problem, because sensors normally generate modified gray code with only one output changing at a time, but rise and fall times must be shorter than 20 $\mu s$ for correct tachometer operation. Motors with 60 electrical degree position sensor coding can be used if one or two of the position sensor signals is inverted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

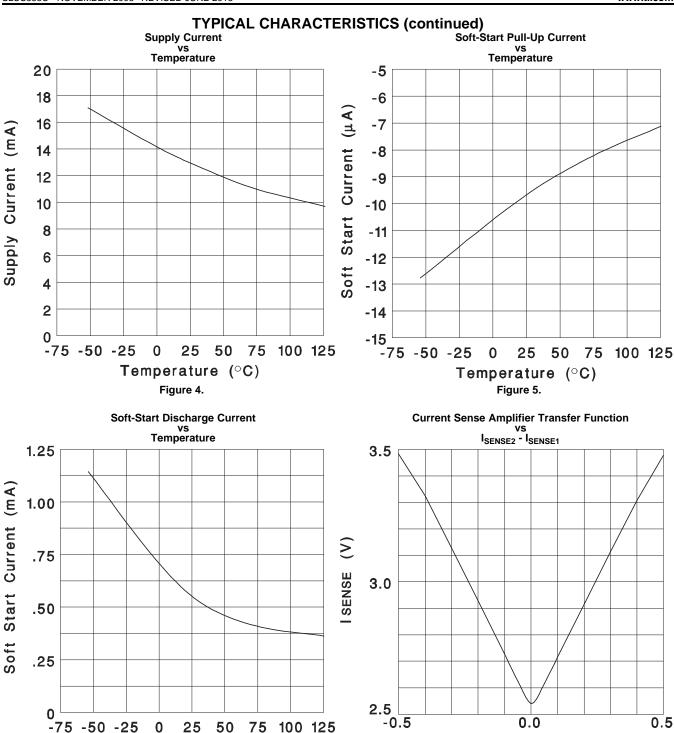

| ISENSE1, ISENSE2,<br>ISENSE              | 3, 4, 5          |     | The current sense amplifier has a fixed gain of approximately two. It also has a built-in level shift of approximately 2.5 V. The signal appearing on ISENSE is: $I_{SENSE} = 2.5 \text{ V} + (2 \times \text{ABS} \text{ (} I_{SENSE1} - I_{SENSE2}) \text{ )}$ $I_{SENSE1}$ and $I_{SENSE2}$ are interchangeable and can be used as differential inputs. The differential signal applied can be as high as $\pm 0.5 \text{ V}$ before saturation. If spikes are expected on ISENSE1 or ISENSE2, they are best filtered by a capacitor from ISENSE to ground. Filtering this way allows fast signal inversions to be correctly processed by the absolute value circuit. The peak-current comparator allows the PWM to enter a current-limit mode with current in the windings never exceeding approximately $0.2 \text{ V} / R_{SENSE}$ . The overcurrent comparator provides a fail-safe shutdown in the unlikely case of current exceeding $0.3 \text{ V} / R_{SENSE}$ . Then, softstart is commanded, and all outputs are turned off until the high current condition is removed. It is often essential to use some filter driving ISENSE1 and ISENSE2 to reject extreme spikes and to control slew rate. Reasonable starting values for filter components might be $250 \cdot \Omega$ series resistors and a 5-nF capacitor between ISENSE1 and ISENSE2. Input resistors should be kept small and matched to maintain gain accuracy. |

| OV-COAST                                 | 23               |     | This input can be used as an over-voltage shut-down input, as a coast input, or both. This input can be driven by TTL, 5-V CMOS, or 12-V CMOS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

# **Terminal Functions (continued)**

| TERMINA       | AL         |     | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------|------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME          | NO.        | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

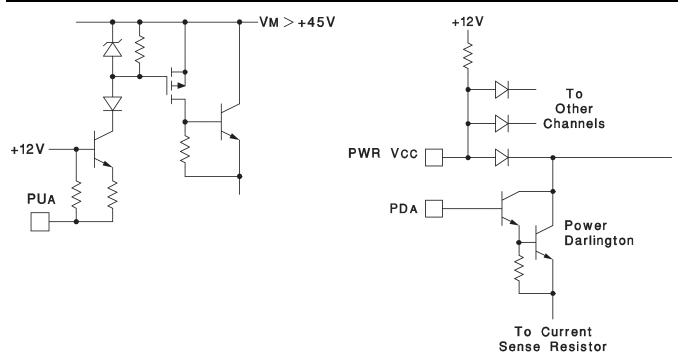

| PDA, PDB, PDC | 12, 13, 14 |     | These outputs can drive the gates of N-channel power MOSFETs directly or they can drive the bases of power Darlingtons if some form of current limiting is used. They are meant to drive low-side power devices in high-current output stages. Current available from these pins can peak as high as 0.5 A. These outputs feature a true totem-pole output stage. Beware of exceeding device power dissipation limits when using these outputs for high continuous currents. These outputs pull high to turn a "low-side" device on (active high).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| PUA, PUB, PUC | 16, 17, 18 |     | These outputs are open-collector, high-voltage drivers that are meant to drive high-side power devices in high-current output stages. These are active low outputs, meaning that these outputs pull low to command a high-side device on. These outputs can drive low-voltage PNP Darlingtons and P-channel MOSFETs directly, and can drive any high-voltage device using external charge pump techniques, transformer signal coupling, cascode level-shift transistors, or opto-isolated drive (high-speed opto-devices are recommended). (See applications).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| PWR VCC       | 11         |     | This supply pin carries the current sourced by the PD outputs. When connecting PD outputs directly to the bases of power Darlingtons, the PWR VCC pin can be current limited with a resistor. Darlington outputs can also be "Baker Clamped" with diodes from collectors back to PWR VCC. (See Applications)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| QUAD SEL      | 22         |     | The device can chop power devices in either of two modes, referred to as "two-quadrant" (Quad Sellow) and <i>four quadrant</i> (Quad Sel high). When two-quadrant chopping, the pull-down power devices are chopped by the output of the PWM latch while the pull-up drivers remain on. The load chops into one commutation diode, and except for back-EMF, will exhibit slow discharge current and faster charge current. Two-quadrant chopping can be more efficient than four-quadrant. When four-quadrant chopping, all power drivers are chopped by the PWM latch, causing the load current to flow into two diodes during chopping. This mode exhibits better control of load current when current is low, and is preferred in servo systems for equal control over acceleration and deceleration. The QUAD SEL input has no effect on operation during braking.                                                                                                                                                                                                                                                                                                                                                                                                                                               |

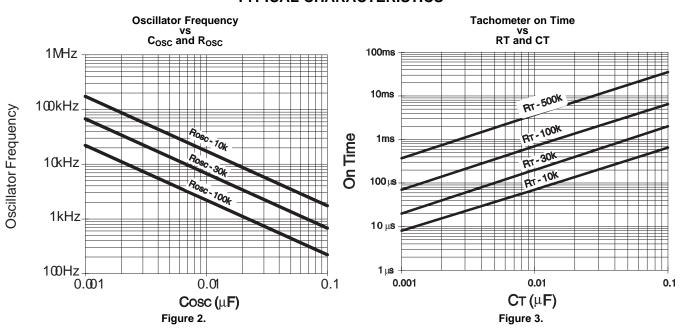

| RC-BRAKE      | 21         |     | Each time the TACH-OUT pulses, the capacitor tied to RC-BRAKE discharges from approximately 3.33 V down to 1.67 V through a resistor. The tachometer pulse width is approximately T = 0.67 $R_T$ $C_T$ , where $R_T$ and $C_T$ are a resistor and capacitor from RC-BRAKE to ground. Recommended values for $R_T$ are 10 $k\Omega$ to 500 $k\Omega$ , and recommended values for $C_T$ are 1 nF to 100 nF, allowing times between 5 $\mu$ s and 10 ms. Best accuracy and stability are achieved with values in the centers of those ranges. RC-BRAKE also has another function. If RC-BRAKE pin is pulled below the brake threshold, the device enters brake mode. This mode consists of turning off all three high-side devices, enabling all three low-side devices, and disabling the tachometer. The only things that inhibit low-side device operation in braking are low-supply, exceeding peak current, OV-COAST command, and the PWM comparator signal. The last of these means that if current sense is implemented such that the signal in the current sense amplifier is proportional to braking current, the low-side devices will brake the motor with current control. (See applications) Simpler current sense connections results in uncontrolled braking and potential damage to the power devices. |

| RC-OSC        | 25         |     | The UC3625 can regulate motor current using fixed-frequency pulse width modulation (PWM). The RC-OSC pin sets oscillator frequency by means of timing resistor $R_{\rm OSC}$ from the RC-OSC pin to VREF and capacitor COSC from RC-OSC to Gnd. Resistors 10 k $\Omega$ to 100 k $\Omega$ and capacitors 1 nF to 100 nF works the best, but frequency should always be below 500 kHz. Oscillator frequency is approximately: $F = 2 / \left( R_{\rm OSC} \times C_{\rm OSC} \right)$ Additional components can be added to this device to cause it to operate as a fixed off-time PWM rather than a fixed frequency PWM, using the RC-OSC pin to select the monostable time constant. The voltage on the RC-OSC pin is normally a ramp of about 1.2-V peak-to-peak, centered at approximately 1.6 V. This ramp can be used for voltage-mode PWM control, or can be used for slope compensation in current-mode control.                                                                                                                                                                                                                                                                                                                                                                                              |

Submit Documentation Feedback

## **Terminal Functions (continued)**

| TERMINA  | TERMINAL AME NO. |     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------|------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME     | NO.              | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| SSTART   | 24               |     | Any time that VCC drops below threshold or the sensed current exceeds the overcurrent threshold, the soft-start latch is set. When set, it turns on a transistor that pulls down on SSTART. Normally, a capacitor is connected to this pin, and the transistor will completely discharge the capacitor. A comparator senses when the NPN transistor has completely discharged the capacitor, and allows the soft-start latch to clear when the fault is removed. When the fault is removed, the soft-start capacitor charges from the on-chip current source. SSTART clamps the output of the error amplifier, not allowing the error amplifier output voltage to exceed SSTART regardless of input. The ramp on RC-OSC can be applied to PWM In and compared to E/A OUT. With SSTART discharged below 0.2 V and the ramp minimum being approximately 1.0 V, the PWM comparator keeps the PWM latch cleared and the outputs off. As SSTART rises, the PWM comparator begins to duty-cycle modulate the PWM latch until the error amplifier inputs overcome the clamp. This provides for a safe and orderly motor start-up from an off or fault condition. A 51-k $\Omega$ resister is added between VREF and SSTART to ensure switching. |

| TACH-OUT | 20               |     | Any change in the H1, H2, or H3 inputs loads data from these inputs into the position sensor latches. At the same time data is loaded, a fixed-width 5-V pulse is triggered on TACH-OUT. The average value of the voltage on TACH-OUT is directly proportional to speed, so this output can be used as a true tachometer for speed feedback with an external filter or averaging circuit which usually consists of a resistor and capacitor.  Whenever TACH-OUT is high, the position latches are inhibited, such that during the noisiest part of the commutation cycle, additional commutations are not possible. Although this effectively sets a maximum rotational speed, the maximum speed can be set above the highest expected speed, preventing false commutation and chatter.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| VCC      | 19               |     | This device operates with supplies between 10 V and 18 V. Under-voltage lockout keeps all outputs off below 7.5 V, insuring that the output transistors never turn on until full drive capability is available. Bypass VCC to ground with an 0.1-µF ceramic capacitor. Using a 10-µF electrolytic bypass capacitor as well can be beneficial in applications with high supply impedance.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| VREF     | 2                |     | This pin provides regulated 5 V for driving Hall-effect devices and speed control circuitry. VREF reaches 5 V before VCC enables, ensuring that Hall-effect devices powered from VREF becomes active before the UC3625 drives any output. Although VREF is current limited, operation over 30 mA is not advised. For proper performance VREF should be bypassed with at least a 0.1-µF capacitor to ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

# TYPICAL CHARACTERISTICS

Temperature (°C) Figure 6. ISENSE2 - ISENSE1 (V)

Figure 7.

#### APPLICATION INFORMATION

#### **Cross Conduction Prevention**

The UC3625 inserts delays to prevent cross conduction due to overlapping drive signals. However, some thought must always be given to cross conduction in output stage design because no amount of dead time can prevent fast slewing signals from coupling drive to a power device through a parasitic capacitance.

The UC3625 contains input latches that serve as noise blanking filters. These latches remain transparent through any phase of a motor rotation and latch immediately after an input transition is detected. They remain latched for two cycles of the PWM oscillator. At a PWM oscillator speed of 20 kHz, this corresponds to 50  $\mu$ s to 100  $\mu$ s of blank time which limits maximum rotational speed to 100 kRPM for a motor with six transitions per rotation or 50 kRPM for a motor with 12 transitions per rotation.

This prevents noise generated in the first 50  $\mu$ s of a transition from propagating to the output transistors and causing cross-conduction or chatter.

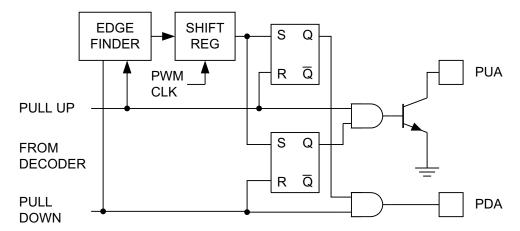

The UC3625 also contains six flip flops corresponding to the six output drive signals. One of these flip flops is set every time that an output drive signal is turned on, and cleared two PWM oscillator cycles after that drive signal is turned off. The output of each flip flop is used to inhibit drive to the opposing output (Figure 8). In this way, it is impossible to turn on driver PUA and PDA at the same time. It is also impossible for one of these drivers to turn on without the other driver having been off for at least two PWM oscillator clocks.

**Figure 8. Cross Conduction Prevention**

#### **Power Stage Design**

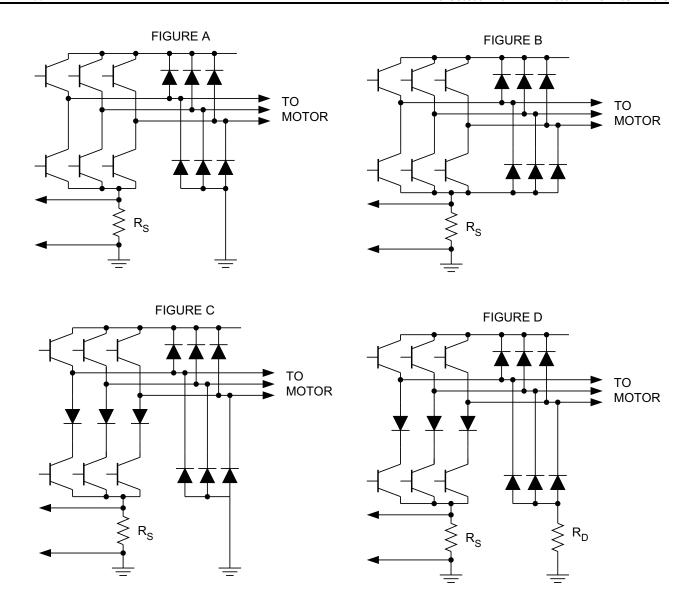

The UC3625 is useful in a wide variety of applications, including high-power in robotics and machinery. The power output stages used in such equipment can take a number of forms, according to the intended performance and purpose of the system. Figure 9 show four different power stages with the advantages and disadvantages of each.

For high-frequency chopping, fast recovery circulating diodes are essential. Six are required to clamp the windings. These diodes should have a continuous current rating at least equal to the operating motor current, since diode conduction duty-cycle can be high. For low-voltage systems, Schottky diodes are preferred. In higher voltage systems, diodes such as Microsemi UHVP high voltage platinum rectifiers are recommended.

In a pulse-by-pulse current control arrangement, current sensing is done by resistor  $R_S$ , through which the transistor's currents are passed (Figure A, Figure B, and Figure C of Figure 9). In these cases,  $R_D$  is not needed. The low-side circulating diodes go to ground and the current sense terminals of the UC3625 ( $I_{SENSE1}$  and  $I_{SENSE2}$ ) are connected to  $R_S$  through a differential RC filter. The input bias current of the current sense amplifier causes a common mode offset voltage to appear at both inputs, so for best accuracy, keep the filter resistors below 2 k $\Omega$  and matched.

The current that flows through  $R_S$  is discontinuous because of chopping. It flows during the on time of the power stage and is zero during the off time. Consequently, the voltage across  $R_S$  consists of a series of pulses, occurring at the PWM frequency, with a peak value indicative of the peak motor current.

To sense average motor current instead of peak current, add another current sense resistor ( $R_D$  in Figure D of Figure 9) to measure current in the low-side circulating diodes, and operate in four quadrant mode (pin 22 high). The negative voltage across  $R_D$  is corrected by the absolute value current sense amplifier. Within the limitations imposed by Table 1, the circuit of Figure B can also sense average current.

Figure 9. Four Power Stage Designs

Table 1. Imposed limitations for Figure 9

|          | 2 QUADRANT | 4 QUADRANT | SAFE    | POWER REVERSE       | CURREN         | T SENSE |

|----------|------------|------------|---------|---------------------|----------------|---------|

|          | 2 QUADRANT | 4 QUADRANI | BRAKING | POWER REVERSE       | Pulse-by-Pulse | Average |

| Figure A | Yes        | No         | No      | N0                  | Yes            | No      |

| Figure B | Yes        | Yes        | No      | In 4-quad mode only | Yes            | Yes     |

| Figure C | Yes        | Yes        | Yes     | In 4-quad mode only | Yes            | No      |

| Figure D | Yes        | Yes        | Yes     | In 4-quad mode only | Yes            | Yes     |

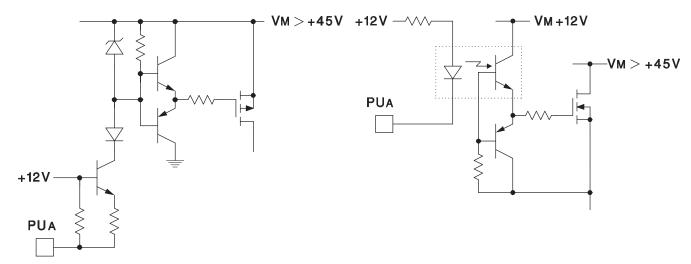

For drives where speed is critical, P-Channel MOSFETs can be driven by emitter followers as shown in Figure 10. Here, both the level shift NPN and the PNP must withstand high voltages. A zener diode is used to limit gate-source voltage on the MOSFET. A series gate resistor is not necessary, but always advisable to control overshoot and ringing.

High-voltage optocouplers can quickly drive high-voltage MOSFETs if a boost supply of at least 10 V greater than the motor supply is provided (See Figure 11) To protect the MOSFET, the boost supply should not be higher than 18 V above the motor supply.

For under 200-V 2-quadrent applications, a power NPN driven by a small P-Channel MOSFET performs well as a high-side driver as in Figure 12. A high voltage small-signal NPN is used as a level shift and a high voltage low-current MOSFET provides drive. Although the NPN will not saturate if used within its limitations, the base-emitter resistor on the NPN is still the speed limiting component.

Figure 13 shows a power NPN Darlington drive technique using a clamp to prevent deep saturation. By limiting saturation of the power device, excessive base drive is minimized and turn-off time is kept fairly short. Lack of base series resistance also adds to the speed of this approach.

Figure 10. Fast High-Side P-Channel Driver

Figure 11. Optocoupled N-Channel High-Side Driver

Figure 12. Power NPN High-Side Driver

Figure 13. Power NPN Low-Side Driver

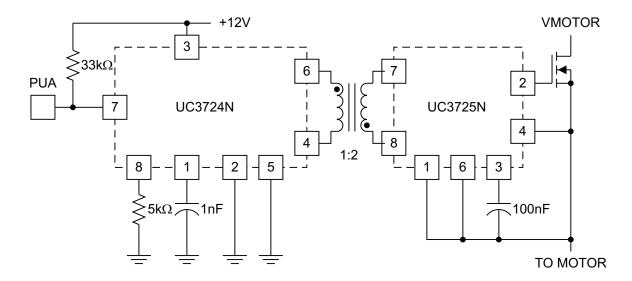

### Fast High-Side N-Channel Driver with Transformer Isolation

A small pulse transformer can provide excellent isolation between the UC3625 and a high-voltage N-Channel MOSFET while also coupling gate drive power. In this circuit (shown in Figure 14), a UC3724 is used as a transformer driver/encoder that duty-cycle modulates the transformer with a 150-kHz pulse train. The UC3725 rectifies this pulse train for gate drive power, demodulates the signal, and drives the gate with over 2-A peak current.

Figure 14. Fast High-Side N-Channel Driver with Transformer Isolation

Both the UC3724 and the UC3725 can operate up to 500 kHz if the pulse transformer is selected appropriately. To raise the operating frequency, either lower the timing resistor of the UC3724 (1 k $\Omega$  min), lower the timing capacitor of the UC3724 (500 pF min) or both.

If there is significant capacitance between transformer primary and secondary, together with very high output slew rate, then it may be necessary to add clamp diodes from the transformer primary to 12 V and ground. General purpose small signal switching diodes such as 1N4148 are normally adequate.

The UC3725 also has provisions for MOSFET current limiting. Consult the UC3725 data sheet for more information on implementing this.

### **Computational Truth Table**

Table 2 shows the outputs of the gate drive and open collector outputs for given hall input codes and direction signals. Numbers at the top of the columns are pin numbers.

These devices operate with position sensor encoding that has either one or two signals high at a time, never all low or all high. This coding is sometimes referred to as 120° Coding because the coding is the same as coding with position sensors spaced 120 magnetic degrees about the rotor. In response to these position sense signals, only one low-side driver turns on (go high) and one high-side driver turns on (pull low) at any time.

**Table 2. Computational Truth Table**

|     | INP | UTS |    |    |          | OUTI | PUTS |           |    |

|-----|-----|-----|----|----|----------|------|------|-----------|----|

| DIR | H1  | H2  | Н3 |    | Low-Side |      |      | High-Side |    |

| 6   | 8   | 9   | 10 | 12 | 13       | 14   | 16   | 17        | 18 |

| 1   | 0   | 0   | 1  | L  | Н        | L    | L    | Н         | Н  |

| 1   | 0   | 1   | 1  | L  | L        | Н    | L    | Н         | Н  |

| 1   | 0   | 1   | 0  | L  | L        | Н    | Н    | L         | Н  |

| 1   | 1   | 1   | 0  | Н  | L        | L    | Н    | L         | Н  |

| 1   | 1   | 0   | 0  | Н  | L        | L    | Н    | Н         | L  |

| 1   | 1   | 0   | 1  | L  | Н        | L    | Н    | Н         | L  |

| 0   | 1   | 0   | 1  | L  | L        | Н    | Н    | L         | Н  |

| 0   | 1   | 0   | 0  | L  | L        | Н    | L    | Н         | Н  |

| 0   | 1   | 1   | 0  | L  | Н        | L    | L    | Н         | Н  |

| 0   | 0   | 1   | 0  | L  | Н        | L    | Н    | Н         | L  |

| 0   | 0   | 1   | 1  | Н  | L        | L    | Н    | Н         | L  |

| 0   | 0   | 0   | 1  | Н  | L        | L    | Н    | L         | Н  |

| Х   | 1   | 1   | 1  | L  | L        | L    | Н    | Н         | Н  |

| Χ   | 0   | 0   | 0  | L  | L        | L    | Н    | Н         | Н  |

Figure 15. 45-V/8-A Brushless DC Motor Drive Circuit

N-Channel power MOSFETs are used for low-side drivers, while P-Channel power MOSFETs are shown for high-side drivers. Resistors are used to level shift the UC3625 open-collector outputs, driving emitter followers into the MOSFET gate. A 12-V zener clamp insures that the MOSFET gate-source voltage never exceeds 12 V. Series  $10-\Omega$  gate resistors tame gate reactance, preventing oscillations and minimizing ringing.

The oscillator timing capacitor should be placed close to pins 15 and 25, to keep ground current out of the capacitor. Ground current in the timing capacitor causes oscillator distortion and slaving to the commutation signal.

The potentiometer connected to pin 1 controls PWM duty cycle directly, implementing a crude form of speed control. This control is often referred to as "voltage mode" because the potentiometer position sets the average motor voltage. This controls speed because steady-state motor speed is closely related to applied voltage.

Pin 20 (Tach-Out) is connected to pin 7 (SPEED IN) through an RC filter, preventing direction reversal while the motor is spinning quickly. In two-quadrant operation, this reversal can cause kinetic energy from the motor to be forced into the power MOSFETs.

A diode in series with the low-side MOSFETs facilitates PWM current control during braking by insuring that braking current will not flow backwards through low-side MOSFETs. Dual current-sense resistors give continuous current sense, whether braking or running in four-quadrant operation, an unnecessary luxury for two-quadrant operation.

The  $68-k\Omega$  and 3-nF tachometer components set maximum commutation time at 140  $\mu$ s. This permits smooth operation up to 35,000 RPM for four-pole motors, yet gives 140  $\mu$ s of noise blanking after commutation.

## www.ti.com

## **REVISION HISTORY**

| C | hanges from Revision B (April 2007) to Revision C                                   | Page |

|---|-------------------------------------------------------------------------------------|------|

| • | Added Storage Temperature and temperature range to Absolute Maximum Ratings Table . | 2    |

10-Dec-2020

#### **PACKAGING INFORMATION**

| Orderable Device | Status (1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp       | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|------------|--------------|--------------------|------|----------------|--------------|-------------------------------|---------------------|--------------|-------------------------|---------|

| UC2625DW         | ACTIVE     | SOIC         | DW                 | 28   | 20             | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 85    | UC2625DW                | Samples |

| UC2625DWG4       | ACTIVE     | SOIC         | DW                 | 28   | 20             | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 85    | UC2625DW                | Samples |

| UC2625DWTR       | ACTIVE     | SOIC         | DW                 | 28   | 1000           | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 85    | UC2625DW                | Samples |

| UC3625DW         | ACTIVE     | SOIC         | DW                 | 28   | 20             | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | 0 to 70      | UC3625DW                | Samples |

| UC3625DWTR       | ACTIVE     | SOIC         | DW                 | 28   | 1000           | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | 0 to 70      | UC3625DW                | Samples |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

## **PACKAGE OPTION ADDENDUM**

10-Dec-2020

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### OTHER QUALIFIED VERSIONS OF UC2625:

● Enhanced Product: UC2625-EP

NOTE: Qualified Version Definitions:

• Enhanced Product - Supports Defense, Aerospace and Medical Applications

PACKAGE MATERIALS INFORMATION

www.ti.com 29-May-2013

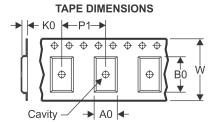

## TAPE AND REEL INFORMATION

|   |    | Dimension designed to accommodate the component width     |

|---|----|-----------------------------------------------------------|

| E | 30 | Dimension designed to accommodate the component length    |

| K | (0 | Dimension designed to accommodate the component thickness |

|   | Ν  | Overall width of the carrier tape                         |

| F | 21 | Pitch between successive cavity centers                   |

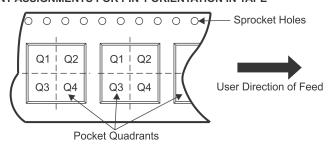

## QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device     | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| UC2625DWTR | SOIC            | DW                 | 28 | 1000 | 330.0                    | 32.4                     | 11.35      | 18.67      | 3.1        | 16.0       | 32.0      | Q1               |

| UC3625DWTR | SOIC            | DW                 | 28 | 1000 | 330.0                    | 32.4                     | 11.35      | 18.67      | 3.1        | 16.0       | 32.0      | Q1               |

**PACKAGE MATERIALS INFORMATION**

www.ti.com 29-May-2013

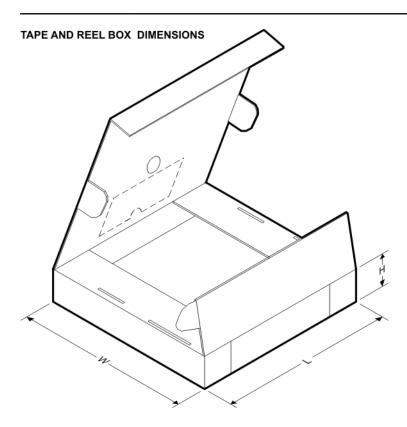

#### \*All dimensions are nominal

| Device     | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|------------|--------------|-----------------|------|------|-------------|------------|-------------|

| UC2625DWTR | SOIC         | DW              | 28   | 1000 | 367.0       | 367.0      | 55.0        |

| UC3625DWTR | SOIC         | DW              | 28   | 1000 | 367.0       | 367.0      | 55.0        |

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

Tl's products are provided subject to Tl's Terms of Sale (<a href="www.ti.com/legal/termsofsale.html">www.ti.com/legal/termsofsale.html</a>) or other applicable terms available either on ti.com or provided in conjunction with such Tl products. Tl's provision of these resources does not expand or otherwise alter Tl's applicable warranties or warranty disclaimers for Tl products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2020, Texas Instruments Incorporated