### **NXP Semiconductors**

Data Sheet: Technical Data

Document Number: MCF54455

Rev. 9, 04/2021

# MCF54455

# MCF5445x ColdFire<sup>®</sup> Microprocessor Data Sheet

#### Features

- Version 4 ColdFire® Core with MMU and EMAC

- Up to 410 Dhrystone 2.1 MIPS @ 266 MHz

- 16-KBytes instruction cache and 16-KBytes data cache

- 32-KBytes internal SRAM

- Support for booting from SPI-compatible flash, EEPROM, and FRAM devices

- Crossbar switch technology (XBS) for concurrent access to peripherals or RAM from multiple bus masters

- 16-channel DMA controller

- 16-bit 133-MHz DDR/mobile-DDR/DDR2 controller

- USB 2.0 On-the-Go controller with ULPI support

- 32-bit PCI controller @ 66MHz

- ATA/ATAPI controller

- 2 10/100 Ethernet MACs

- Coprocessor for acceleration of the DES, 3DES, AES, MD5, and SHA-1 algorithms

- Random number generator

- Synchronous serial interface (SSI)

- 4 periodic interrupt timers (PIT)

- 4 32-bit timers with DMA support

- DMA-supported serial peripheral interface (DSPI)

- 3 UARTs

- I<sup>2</sup>C bus interface

NP

NXP reserves the right to change the production detail specifications as may be required to permit improvements in the design of its products.

# **Table of Contents**

| 1 | MCF   | 5445x Family Comparison           |   | 5.9.1 Overshoot and Undershoot 2                       | 28 |

|---|-------|-----------------------------------|---|--------------------------------------------------------|----|

| 2 |       | ring Information5                 |   | 5.10 ULPI Timing Specifications                        | 29 |

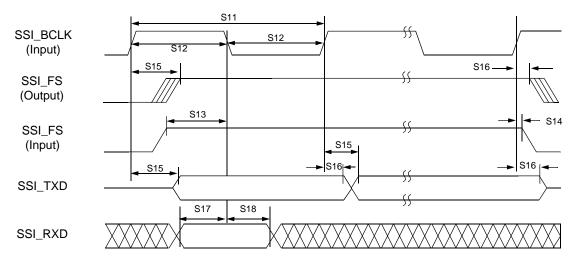

| 3 | Hard  | ware Design Considerations5       |   | 5.11 SSI Timing Specifications                         |    |

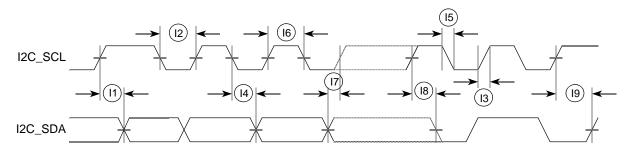

|   | 3.1   | Analog Power Filtering            |   | 5.12 I <sup>2</sup> C Timing Specifications            |    |

|   | 3.2   | Oscillator Power Filtering        |   | 5.13 Fast Ethernet Timing Specifications               |    |

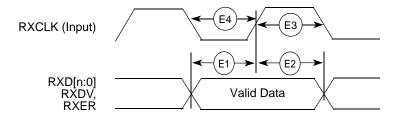

|   | 3.3   | Supply Voltage Sequencing         |   | 5.13.1 Receive Signal Timing Specifications 3          |    |

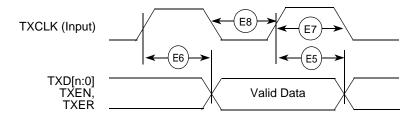

|   |       | 3.3.1 Power-Up Sequence           |   | 5.13.2 Transmit Signal Timing Specifications 3         | 4  |

|   |       | 3.3.2 Power-Down Sequence7        |   | 5.13.3 Asynchronous Input Signal Timing                |    |

| 4 | Pin A | ssignments and Reset States7      |   | Specifications                                         | 34 |

|   | 4.1   | Signal Multiplexing               |   | 5.13.4 MII Serial Management Timing Specifications . 3 | 55 |

|   | 4.2   | Pinout—256 MAPBGA                 |   | 5.14 32-Bit Timer Module Timing Specifications         | 5  |

|   | 4.3   | Pinout—360 TEPBGA                 |   | 5.15 ATA Interface Timing Specifications               | 6  |

| 5 | Elect | rical Characteristics17           |   | 5.16 DSPI Timing Specifications                        | 36 |

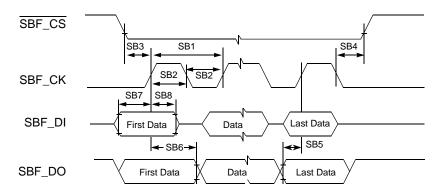

|   | 5.1   | Absolute Maximum Ratings          |   | 5.17 SBF Timing Specifications                         |    |

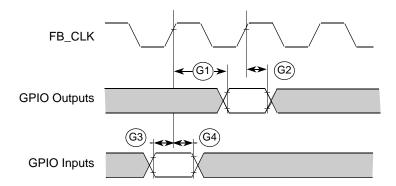

|   | 5.2   | Thermal Characteristics           |   | 5.18 General Purpose I/O Timing Specifications 3       | 39 |

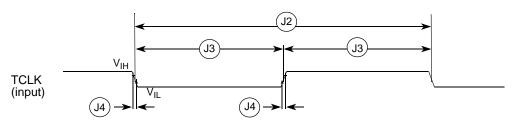

|   | 5.3   | ESD Protection                    |   | 5.19 JTAG and Boundary Scan Timing 4                   | 0  |

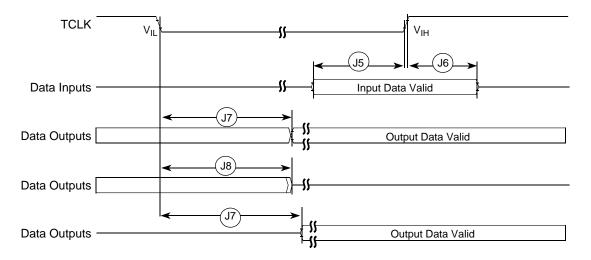

|   | 5.4   | DC Electrical Specifications      |   | 5.20 Debug AC Timing Specifications 4                  |    |

|   | 5.5   | ClockTiming Specifications        | 6 | Power Consumption                                      | 3  |

|   | 5.6   | Reset Timing Specifications       | 7 | 7 Package Information                                  |    |

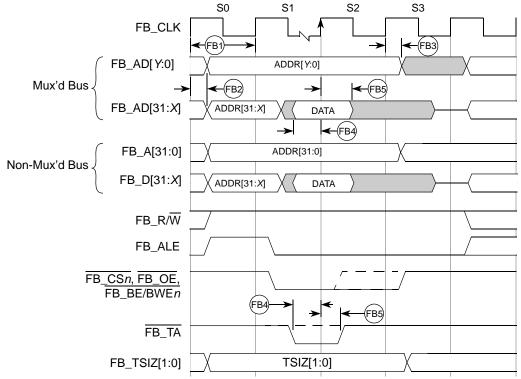

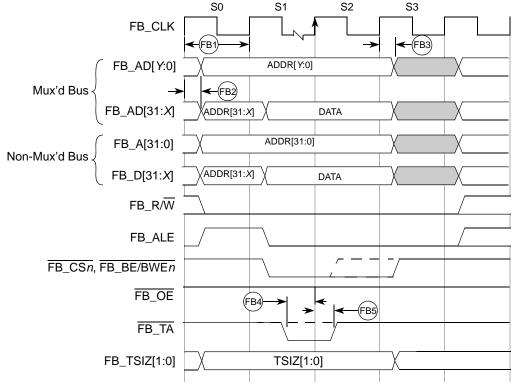

|   | 5.7   | FlexBus Timing Specifications     | 8 | Product Documentation4                                 | 5  |

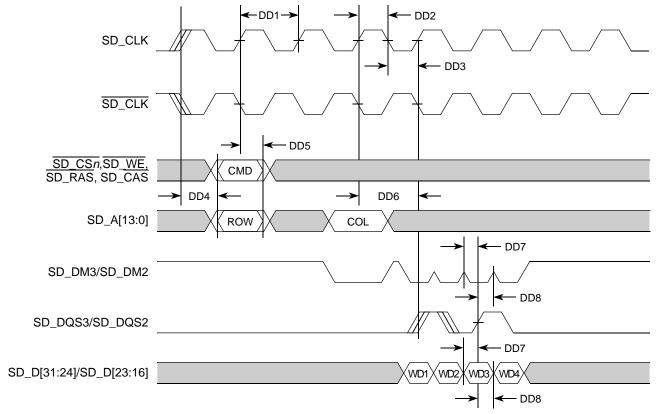

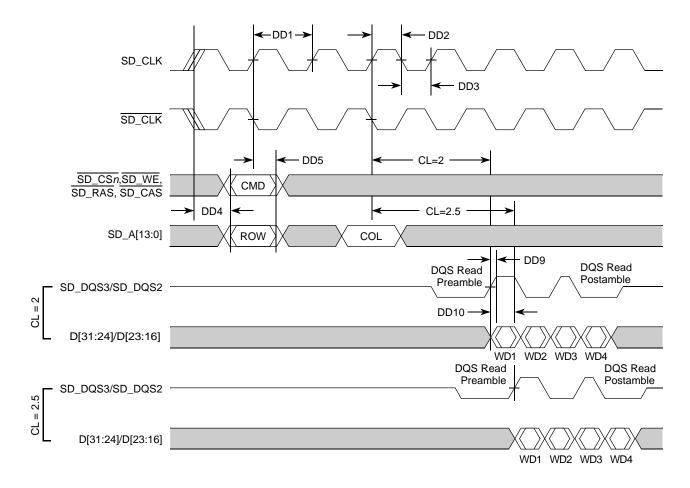

|   | 5.8   | SDRAM AC Timing Characteristics25 | 9 |                                                        |    |

|   | 5.9   | PCI Bus Timing Specifications 27  |   | •                                                      |    |

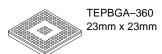

Figure 1. MCF54455 Block Diagram

USB OTG - Universal Serial Bus On-the-Go controller

I<sup>2</sup>C

- Inter-Intergrated Circuit

# 1 MCF5445x Family Comparison

The following table compares the various device derivatives available within the MCF5445x family.

Table 1. MCF5445x Family Configurations

| Module                                                                | MCF54450 | MCF54451 | MCF54452     | MCF54453 | MCF54454 | MCF54455 |  |

|-----------------------------------------------------------------------|----------|----------|--------------|----------|----------|----------|--|

| ColdFire Version 4 Core with EMAC (Enhanced Multiply-Accumulate Unit) | •        | •        | •            | •        | •        | •        |  |

| Core (System) Clock                                                   | up to 2  | 40 MHz   |              | up to 20 | 66 MHz   |          |  |

| Peripheral Bus Clock<br>(Core clock ÷ 2)                              | up to 1  | 20 MHz   |              | up to 1  | 33 MHz   |          |  |

| External Bus Clock<br>(Core clock ÷ 4)                                | up to 6  | 60 MHz   | up to 66 MHz |          |          |          |  |

| Performance (Dhrystone/2.1 MIPS)                                      | up to    | 370      |              | up to    | 410      |          |  |

| Independent Data/Instruction Cache                                    |          |          | 16 Kbyt      | es each  |          |          |  |

| Static RAM (SRAM)                                                     |          |          | 32 K         | bytes    |          |          |  |

| PCI Controller                                                        | _        | _        | •            | •        | •        | •        |  |

| Cryptography Acceleration Unit (CAU)                                  | _        | •        | _            | •        | _        | •        |  |

| ATA Controller                                                        | _        | _        | _            | _        | •        | •        |  |

| DDR SDRAM Controller                                                  | •        | •        | •            | •        | •        | •        |  |

| FlexBus External Interface                                            | •        | •        | •            | •        | •        | •        |  |

| USB 2.0 On-the-Go                                                     | •        | •        | •            | •        | •        | •        |  |

| UTMI+ Low Pin Interface (ULPI)                                        | •        | •        | •            | •        | •        | •        |  |

| Synchronous Serial Interface (SSI)                                    | •        | •        | •            | •        | •        | •        |  |

| Fast Ethernet Controller (FEC)                                        | 1        | 1        | 2            | 2        | 2        | 2        |  |

| UARTs                                                                 | 3        | 3        | 3            | 3        | 3        | 3        |  |

| l <sup>2</sup> C                                                      | •        | •        | •            | •        | •        | •        |  |

| DSPI                                                                  | •        | •        | •            | •        | •        | •        |  |

| Real Time Clock                                                       | •        | •        | •            | •        | •        | •        |  |

| 32-bit DMA Timers                                                     | 4        | 4        | 4            | 4        | 4        | 4        |  |

| Watchdog Timer (WDT)                                                  | •        | •        | •            | •        | •        | •        |  |

| Periodic Interrupt Timers (PIT)                                       | 4        | 4        | 4            | 4        | 4        | 4        |  |

| Edge Port Module (EPORT)                                              | •        | •        | •            | •        | •        | •        |  |

| Interrupt Controllers (INTC)                                          | 2        | 2        | 2            | 2        | 2        | 2        |  |

| 16-channel Direct Memory Access (DMA)                                 | •        | •        | •            | •        | •        | •        |  |

| General Purpose I/O (GPIO)                                            | •        | •        | •            | •        | •        | •        |  |

| JTAG - IEEE® 1149.1 Test Access Port                                  | •        | •        | •            | •        | •        | •        |  |

| Package                                                               | 256 M    | APBGA    |              | 360 TE   | PBGA     |          |  |

# 2 Ordering Information

**Table 2. Orderable Part Numbers**

| Part Number    | Description                  | Package     | Speed   | Temperature    |

|----------------|------------------------------|-------------|---------|----------------|

| MCF54450CVM180 | MCF54450 Microprocessor      |             | 180 MHz | –40° to +85° C |

| MCF54450VM240  | Wici 34430 Wicioprocessor    | 256 MAPBGA  | 240 MHz | 0° to +70° C   |

| MCF54451CVM180 | MCF54451 Microprocessor      | 230 MAI DOA | 180 MHz | –40° to +85° C |

| MCF54451VM240  | Wildi 34431 Wildioprocessor  |             | 240 MHz | 0° to +70° C   |

| MCF54452CVP200 | MCF54452 Microprocessor      |             | 200 MHz | –40° to +85° C |

| MCF54452VP266  |                              |             | 266 MHz | 0° to +70° C   |

| MCF54453CVP200 | MCF54453 Microprocessor      |             | 200 MHz | –40° to +85° C |

| MCF54453VP266  | Wildi 34403 Microprocessor   | 360 TEPBGA  | 266 MHz | 0° to +70° C   |

| MCF54454CVP200 | MCF54454 Microprocessor      | JOO ILI DOA | 200 MHz | –40° to +85° C |

| MCF54454VP266  | Wei offer Microprocessor     |             | 266 MHz | 0° to +70° C   |

| MCF54455CVP200 | MCF54455 Microprocessor      |             | 200 MHz | –40° to +85° C |

| MCF54455VP266  | Wildli 34433 Wildloprocessor |             | 266 MHz | 0° to +70° C   |

# 3 Hardware Design Considerations

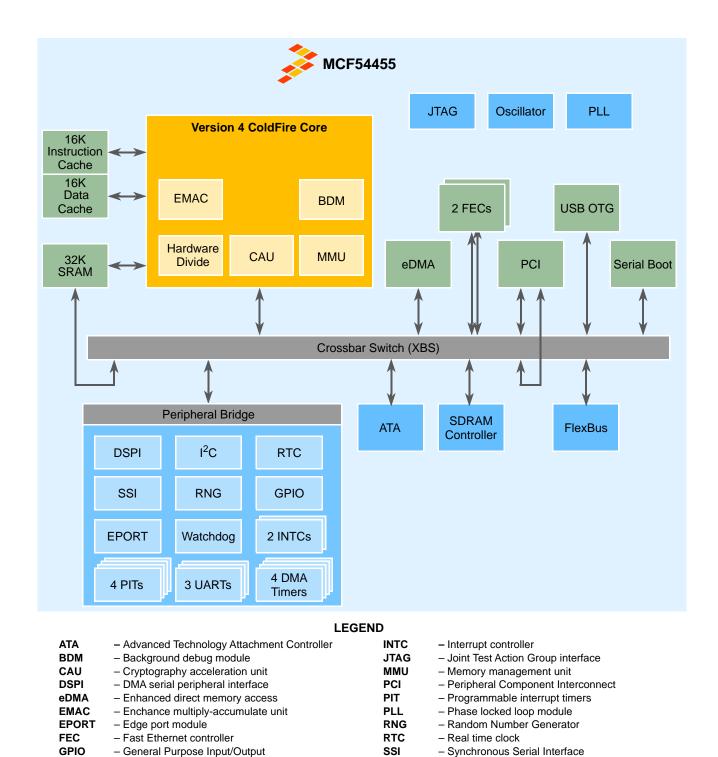

# 3.1 Analog Power Filtering

To further enhance noise isolation, an external filter is strongly recommended for the analog  $V_{DD}$  pins (VDD\_A\_PLL, VDD\_RTC). The filter shown in Figure 2 should be connected between the board  $IV_{DD}$  and the analog pins. The resistor and capacitors should be placed as close to the dedicated analog  $V_{DD}$  pin as possible. The 10- $\Omega$  resistor in the given filter is required. Do not implement the filter circuit using only capacitors. The analog power pins draw very little current. Concerns regarding voltage loss across the 10-ohm resistor are not valid.

Figure 2. System Analog V<sub>DD</sub> Power Filter

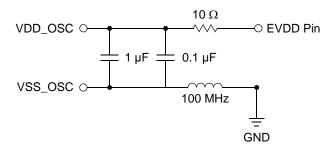

### 3.2 Oscillator Power Filtering

Figure 3 shows an example for isolating the oscillator power supply from the I/O supply (EVDD) and ground.

Figure 3. Oscillator Power Filter

# 3.3 Supply Voltage Sequencing

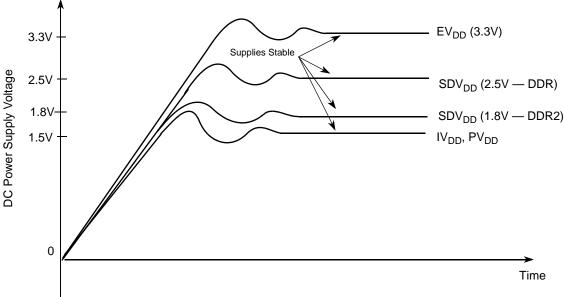

Figure 4 shows situations in sequencing the I/O  $V_{DD}$  (EV $_{DD}$ ), SDRAM  $V_{DD}$  (SDV $_{DD}$ ), PLL  $V_{DD}$  (PV $_{DD}$ ), and internal logic/core  $V_{DD}$  (IV $_{DD}$ ).

Notes

Figure 4. Supply Voltage Sequencing and Separation Cautions

The relationship between  $SDV_{DD}$  and  $EV_{DD}$  is non-critical during power-up and power-down sequences.  $SDV_{DD}$  (2.5V or 1.8V) and  $EV_{DD}$  are specified relative to  $IV_{DD}$ .

Input voltage must not be greater than the supply voltage (EV<sub>DD</sub>, SDV<sub>DD</sub>, IV<sub>DD</sub>, or PV<sub>DD</sub>) by more than 0.5V at any time, including during power-up.

<sup>&</sup>lt;sup>2</sup> Use 50 V/millisecond or slower rise time for all supplies.

#### 3.3.1 Power-Up Sequence

If  $EV_{DD}/SDV_{DD}$  are powered up with the  $IV_{DD}$  at 0 V, the sense circuits in the I/O pads cause all pad output drivers connected to the  $EV_{DD}/SDV_{DD}$  to be in a high impedance state. There is no limit on how long after  $EV_{DD}/SDV_{DD}$  powers up before  $IV_{DD}$  must power up. The rise times on the power supplies should be slower than 50 V/millisecond to avoid turning on the internal ESD protection clamp diodes.

#### 3.3.2 Power-Down Sequence

If  $IV_{DD}/PV_{DD}$  are powered down first, sense circuits in the I/O pads cause all output drivers to be in a high impedance state. There is no limit on how long after  $IV_{DD}$  and  $PV_{DD}$  power down before  $EV_{DD}$  or  $SDV_{DD}$  must power down. There are no requirements for the fall times of the power supplies.

# 4 Pin Assignments and Reset States

FB TA

FB\_TS

### 4.1 Signal Multiplexing

The following table lists all the MCF5445x pins grouped by function. The Dir column is the direction for the primary function of the pin only. Refer to Section 4, "Pin Assignments and Reset States," for package diagrams. For a more detailed discussion of the MCF5445x signals, consult the MCF54455 Reference Manual (MCF54455RM).

#### NOTE

In this table and throughout this document, a single signal within a group is designated without square brackets (i.e., FB\_AD23), while designations for multiple signals within a group use brackets (i.e., FB\_AD[23:21]) and is meant to include all signals within the two bracketed numbers when these numbers are separated by a colon.

#### NOTE

The primary functionality of a pin is not necessarily its default functionality. Most pins that are muxed with GPIO default to their GPIO functionality. See Table 3 for a list of the exceptions.

| Pin            | 256 MAPBGA | 360 TEPBGA                               |  |  |  |

|----------------|------------|------------------------------------------|--|--|--|

| FB_AD[31:0]    |            | n serial boot selects 0-bit<br>ort size. |  |  |  |

| FB_BE/BWE[3:0] | FB_BE/E    | 3WE[3:0]                                 |  |  |  |

| FB_CS[3:1]     | FB_C       | S[3:1]                                   |  |  |  |

| FB_OE          | FB_OE      |                                          |  |  |  |

| FB_R/W         | FB_        | R/W                                      |  |  |  |

FB TA

FB\_TS

Table 3. Special-Case Default Signal Functionality

MCF5445x ColdFire® Microprocessor Data Sheet, Rev. 9, 04/2021

Table 3. Special-Case Default Signal Functionality (continued)

| Pin          | 256 MAPBGA | 360 TEPBGA                           |

|--------------|------------|--------------------------------------|

| PCI_GNT[3:0] | GPIO       | PCI_GNT[3:0]                         |

| PCI_REQ[3:0] | GPIO       | PCI_REQ[3:0]                         |

| ĪRQ1         | GPIO       | PCI_INTA and configured as an agent. |

| ATA_RESET    | GPIO       | ATA reset                            |

Table 4. MCF5445x Signal Information and Muxing

| Signal Name    | GPIO                      | Alternate 1  | Alternate 2 | Pull-up (U) <sup>1</sup><br>Pull-down (D) | Direction <sup>2</sup> | Voltage Domain | MCF54450<br>MCF54451<br>256 MAPBGA           | MCF54452<br>MCF54453<br>MCF54454<br>MCF54455<br>360 TEPBGA |  |  |  |  |

|----------------|---------------------------|--------------|-------------|-------------------------------------------|------------------------|----------------|----------------------------------------------|------------------------------------------------------------|--|--|--|--|

|                | Reset                     |              |             |                                           |                        |                |                                              |                                                            |  |  |  |  |

| RESET          | _                         | _            | _           | U                                         | I                      | EVDD           | L4                                           | Y18                                                        |  |  |  |  |

| RSTOUT         | _                         | _            | _           | _                                         | 0                      | EVDD           | M15                                          | B17                                                        |  |  |  |  |

|                |                           |              | Clock       |                                           |                        |                |                                              |                                                            |  |  |  |  |

| EXTAL/PCI_CLK  | _                         | _            | —           | _                                         | I                      | EVDD           | M16                                          | A16                                                        |  |  |  |  |

| XTAL           | _                         | _            | _           | $U^3$                                     | 0                      | EVDD           | L16                                          | A17                                                        |  |  |  |  |

|                | Mode Selection            |              |             |                                           |                        |                |                                              |                                                            |  |  |  |  |

| BOOTMOD[1:0]   | _                         | _            | _           | _                                         | I                      | EVDD           | M5, M7                                       | AB17, AB21                                                 |  |  |  |  |

|                | FlexBus                   |              |             |                                           |                        |                |                                              |                                                            |  |  |  |  |

| FB_AD[31:24]   | PFBADH[7:0] <sup>4</sup>  | FB_D[31:24]  | _           | _                                         | I/O                    | EVDD           | A14, A13, D12,<br>C12, B12, A12,<br>D11, C11 | J2, K4, J1, K1–3,<br>L1, L4                                |  |  |  |  |

| FB_AD[23:16]   | PFBADMH[7:0] <sup>4</sup> | FB_D[23:16]  | _           | _                                         | I/O                    | EVDD           | B11, A11, D10,<br>C10, B10, A10, D9,<br>C9   | L2, L3, M1–4, N1–<br>2                                     |  |  |  |  |

| FB_AD[15:8]    | PFBADML[7:0] <sup>4</sup> | FB_D[15:8]   | _           | _                                         | I/O                    | EVDD           | B9, A9, D8, C8, B8,<br>A8, D7, C7            | P1–2, R1–3, P4,<br>T1–2                                    |  |  |  |  |

| FB_AD[7:0]     | PFBADL[7:0] <sup>4</sup>  | FB_D[7:0]    | _           | _                                         | I/O                    | EVDD           | B7, A7, D6, C6, B6,<br>A6, D5, C5            | T3-4, U1-3, V1-2,<br>W1                                    |  |  |  |  |

| FB_BE/BWE[3:2] | PBE[3:2]                  | FB_TSIZ[1:0] | _           | _                                         | 0                      | EVDD           | B5, A5                                       | Y1, W2                                                     |  |  |  |  |

| FB_BE/BWE[1:0] | PBE[1:0]                  | _            | _           | _                                         | 0                      | EVDD           | B4, A4                                       | W3, Y2                                                     |  |  |  |  |

| FB_CLK         | _                         | _            | _           | _                                         | 0                      | EVDD           | B13                                          | J3                                                         |  |  |  |  |

| FB_CS[3:1]     | PCS[3:1]                  |              | _           | _                                         | 0                      | EVDD           | C2, D4, C3                                   | W5, AA4, AB3                                               |  |  |  |  |

| FB_CS0         |                           |              |             | _                                         | 0                      | EVDD           | C4                                           | Y4                                                         |  |  |  |  |

| FB_OE          | PFBCTL3                   |              | _           | _                                         | 0                      | EVDD           | A2                                           | AA1                                                        |  |  |  |  |

| FB_R/W         | PFBCTL2                   | _            | _           | _                                         | 0                      | EVDD           | B2                                           | AA3                                                        |  |  |  |  |

| FB_TA          | PFBCTL1                   | _            | _           | U                                         | I                      | EVDD           | B1                                           | AB2                                                        |  |  |  |  |

Table 4. MCF5445x Signal Information and Muxing (continued)

| Signal Name             | GPIO      | Alternate 1  | Alternate 2                | Pull-up (U) <sup>1</sup><br>Pull-down (D) | Direction <sup>2</sup> | Voltage Domain | MCF54450<br>MCF54451<br>256 MAPBGA                                                                    | MCF54452<br>MCF54453<br>MCF54454<br>MCF54455<br>360 TEPBGA                                                                                               |

|-------------------------|-----------|--------------|----------------------------|-------------------------------------------|------------------------|----------------|-------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| FB_TS                   | PFBCTL0   | FB_ALE       | FB_TBST                    | _                                         | 0                      | EVDD           | A3                                                                                                    | Y3                                                                                                                                                       |

|                         |           | PC           | CI Controller <sup>5</sup> |                                           |                        |                |                                                                                                       |                                                                                                                                                          |

| PCI_AD[31:0]            | _         | FB_A[31:0]   | _                          | _                                         | I/O                    | EVDD           | _                                                                                                     | C11, D11, A10,<br>B10, J4, G2, G3,<br>F1, D12, C12, B12,<br>A11, B11, B9, D9,<br>D10, A8, B8, A5,<br>B5, A4, A3, B3, D4,<br>D3, E3-E1, F3, C2,<br>D2, C1 |

| _                       | _         | FB_A[23:0]   | _                          | _                                         | I/O                    | EVDD           | K14-13, J15-13,<br>H13-15, G15-13,<br>F14-13, E15-13,<br>D16, B16, C15,<br>B15, C14, D15,<br>C16, D14 | _                                                                                                                                                        |

| PCI_CBE[3:0]            | _         | <del>_</del> | _                          | _                                         | I/O                    | EVDD           | _                                                                                                     | G4, E4, D1, B1                                                                                                                                           |

| PCI_DEVSEL              | _         | _            | _                          | _                                         | 0                      | EVDD           | _                                                                                                     | F2                                                                                                                                                       |

| PCI_FRAME               | _         | _            | _                          | _                                         | I/O                    | EVDD           | _                                                                                                     | B2                                                                                                                                                       |

| PCI_GNT3                | PPCI7     | ATA_DMACK    | _                          | _                                         | 0                      | EVDD           | _                                                                                                     | В7                                                                                                                                                       |

| PCI_GNT[2:1]            | PPCI[6:5] | _            | _                          | _                                         | 0                      | EVDD           | _                                                                                                     | C8, C9                                                                                                                                                   |

| PCI_GNT0/<br>PCI_EXTREQ | PPCI4     | _            | _                          | _                                         | 0                      | EVDD           | _                                                                                                     | А9                                                                                                                                                       |

| PCI_IDSEL               | _         | _            | _                          | _                                         | I                      | EVDD           | _                                                                                                     | D5                                                                                                                                                       |

| PCI_IRDY                | _         | _            | _                          | _                                         | I/O                    | EVDD           | _                                                                                                     | C3                                                                                                                                                       |

| PCI_PAR                 | _         | _            | _                          | _                                         | I/O                    | EVDD           | _                                                                                                     | C4                                                                                                                                                       |

| PCI_PERR                | _         | _            | _                          | _                                         | I/O                    | EVDD           | _                                                                                                     | B4                                                                                                                                                       |

| PCI_REQ3                | PPCI3     | ATA_INTRQ    | _                          | _                                         | - 1                    | EVDD           | _                                                                                                     | C7                                                                                                                                                       |

| PCI_REQ[2:1]            | PPCI[2:1] | _            | _                          | _                                         | I                      | EVDD           | _                                                                                                     | D7, C5                                                                                                                                                   |

| PCI_REQ0/<br>PCI_EXTGNT | PPCI0     | _            | _                          | _                                         | I                      | EVDD           | _                                                                                                     | A2                                                                                                                                                       |

| PCI_RST                 | _         | _            | _                          | _                                         | 0                      | EVDD           | _                                                                                                     | B6                                                                                                                                                       |

| PCI_SERR                | _         | _            | _                          | _                                         | I/O                    | EVDD           | _                                                                                                     | A6                                                                                                                                                       |

| PCI_STOP                | _         | _            | _                          | _                                         | I/O                    | EVDD           | _                                                                                                     | A7                                                                                                                                                       |

| PCI_TRDY                | _         | _            | _                          | _                                         | I/O                    | EVDD           | _                                                                                                     | C10                                                                                                                                                      |

|                         |           | SDR          | RAM Controller             |                                           |                        |                |                                                                                                       | '                                                                                                                                                        |

| SD_A[13:0]              | _         | _            | _                          | _                                         | 0                      | SDVDD          | R1, P1, N2, P2,<br>R2, T2, M4, N3,<br>P3, R3, T3, T4, R4,<br>N4                                       | V22, U20–22,<br>T19–22, R20–22,<br>N19, P20–21                                                                                                           |

Table 4. MCF5445x Signal Information and Muxing (continued)

| Signal Name   | GPIO        | Alternate 1          | Alternate 2                     | Pull-up (U) <sup>1</sup><br>Pull-down (D) | Direction <sup>2</sup> | Voltage Domain | MCF54450<br>MCF54451<br>256 MAPBGA                                             | MCF54452<br>MCF54453<br>MCF54454<br>MCF54455<br>360 TEPBGA                                 |

|---------------|-------------|----------------------|---------------------------------|-------------------------------------------|------------------------|----------------|--------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| SD_BA[1:0]    | _           | _                    | _                               | _                                         | 0                      | SDVDD          | P4, T5                                                                         | P22, P19                                                                                   |

| SD_CAS        | _           | _                    | _                               | _                                         | 0                      | SDVDD          | T6                                                                             | L19                                                                                        |

| SD_CKE        | _           | _                    | _                               | _                                         | 0                      | SDVDD          | N5                                                                             | N22                                                                                        |

| SD_CLK        | _           | _                    | _                               | _                                         | 0                      | SDVDD          | Т9                                                                             | L22                                                                                        |

| SD_CLK        | _           | _                    | _                               | _                                         | 0                      | SDVDD          | Т8                                                                             | M22                                                                                        |

| SD_CS[1:0]    | _           | _                    | _                               | _                                         | 0                      | SDVDD          | P6, R6                                                                         | L20, M20                                                                                   |

| SD_D[31:16]   | _           | _                    | _                               | _                                         | I/O                    | SDVDD          | N6, T7, N7, P7, R7,<br>R8, P8, N8, N9,<br>T10, R10, P10,<br>N10, T11, R11, P11 | L21, K22, K21,<br>K20, J20, J19, J21,<br>J22, H20, G22,<br>G21, G20, G19,<br>F22, F21, F20 |

| SD_DM[3:2]    | _           | _                    | _                               | _                                         | 0                      | SDVDD          | P9, N12                                                                        | H21, E21                                                                                   |

| SD_DQS[3:2]   | _           | _                    | _                               | _                                         | 0                      | SDVDD          | R9, N11                                                                        | H22, E22                                                                                   |

| SD_RAS        | _           | _                    | _                               | _                                         | 0                      | SDVDD          | P5                                                                             | N21                                                                                        |

| SD_VREF       | _           | _                    | _                               | _                                         | I                      | SDVDD          | M8                                                                             | M21                                                                                        |

| SD_WE         | _           | _                    | _                               | _                                         | 0                      | SDVDD          | R5                                                                             | N20                                                                                        |

|               |             | Externa              | al Interrupts Port <sup>6</sup> |                                           | •                      | •              |                                                                                |                                                                                            |

| ĪRQ7          | PIRQ7       | _                    | _                               | _                                         | I                      | EVDD           | L1                                                                             | ABB13                                                                                      |

| ĪRQ4          | PIRQ4       | _                    | SSI_CLKIN                       | _                                         | I                      | EVDD           | L2                                                                             | ABB13                                                                                      |

| ĪRQ3          | PIRQ3       | _                    | _                               | _                                         | I                      | EVDD           | L3                                                                             | AB14                                                                                       |

| ĪRQ1          | PIRQ1       | PCI_INTA             | _                               | _                                         | I                      | EVDD           | F15                                                                            | C6                                                                                         |

|               | <u> </u>    |                      | FEC0                            |                                           | l                      | ı              | <u> </u>                                                                       | <u> </u>                                                                                   |

| FEC0_MDC      | PFECI2C3    | _                    | _                               | _                                         | 0                      | EVDD           | F3                                                                             | AB8                                                                                        |

| FEC0_MDIO     | PFECI2C2    | _                    | _                               | _                                         | I/O                    | EVDD           | F2                                                                             | Y7                                                                                         |

| FEC0_COL      | PFEC0H4     | _                    | ULPI_DATA7                      | _                                         | ı                      | EVDD           | E1                                                                             | AB7                                                                                        |

| FEC0_CRS      | PFEC0H0     | _                    | ULPI_DATA6                      | _                                         | ı                      | EVDD           | F1                                                                             | AA7                                                                                        |

| FEC0_RXCLK    | PFEC0H3     | _                    | ULPI_DATA1                      | _                                         | ı                      | EVDD           | G1                                                                             | AA8                                                                                        |

| FEC0_RXDV     | PFEC0H2     | FEC0_RMII_<br>CRS_DV | _                               | _                                         | I                      | EVDD           | G2                                                                             | Y8                                                                                         |

| FEC0_RXD[3:2] | PFEC0L[3:2] | _                    | ULPI_DATA[5:4]                  | _                                         | I                      | EVDD           | G3, G4                                                                         | AB9, Y9                                                                                    |

| FEC0_RXD1     | PFEC0L1     | FEC0_RMII_RXD1       | _                               | _                                         | I                      | EVDD           | H1                                                                             | W9                                                                                         |

| FEC0_RXD0     | PFEC0H1     | FEC0_RMII_RXD0       | _                               | _                                         | I                      | EVDD           | H2                                                                             | AB10                                                                                       |

| FEC0_RXER     | PFEC0L0     | FEC0_RMII_RXER       | _                               | _                                         | I                      | EVDD           | H3                                                                             | AA10                                                                                       |

Table 4. MCF5445x Signal Information and Muxing (continued)

| Signal Name   | GPIO        | Alternate 1           | Alternate 2    | Pull-up (U) <sup>1</sup><br>Pull-down (D) | Direction <sup>2</sup> | Voltage Domain | MCF54450<br>MCF54451<br>256 MAPBGA | MCF54452<br>MCF54453<br>MCF54454<br>MCF54455<br>360 TEPBGA |  |  |

|---------------|-------------|-----------------------|----------------|-------------------------------------------|------------------------|----------------|------------------------------------|------------------------------------------------------------|--|--|

| FEC0_TXCLK    | PFEC0H7     | FEC0_RMII_<br>REF_CLK | _              | _                                         | I                      | EVDD           | H4                                 | Y10                                                        |  |  |

| FEC0_TXD[3:2] | PFEC0L[7:6] | _                     | ULPI_DATA[3:2] | _                                         | 0                      | EVDD           | J1, J2                             | W10, AB11                                                  |  |  |

| FEC0_TXD1     | PFEC0L5     | FEC0_RMII_TXD1        | _              | _                                         | 0                      | EVDD           | J3                                 | AA11                                                       |  |  |

| FEC0_TXD0     | PFEC0H5     | FEC0_RMII_TXD0        | _              | _                                         | 0                      | EVDD           | J4                                 | Y11                                                        |  |  |

| FEC0_TXEN     | PFEC0H6     | FEC0_RMII_TXEN        | _              | _                                         | 0                      | EVDD           | K1                                 | W11                                                        |  |  |

| FEC0_TXER     | PFEC0L4     | _                     | ULPI_DATA0     | _                                         | 0                      | EVDD           | K2                                 | AB12                                                       |  |  |

| FEC1          |             |                       |                |                                           |                        |                |                                    |                                                            |  |  |

| FEC1_MDC      | PFECI2C5    | _                     | ATA_DIOR       | _                                         | 0                      | EVDD           | _                                  | W20                                                        |  |  |

| FEC1_MDIO     | PFECI2C4    | _                     | ATA_DIOW       | _                                         | I/O                    | EVDD           | _                                  | Y22                                                        |  |  |

| FEC1_COL      | PFEC1H4     | _                     | ATA_DATA7      | _                                         | I                      | EVDD           | _                                  | AB18                                                       |  |  |

| FEC1_CRS      | PFEC1H0     | _                     | ATA_DATA6      | _                                         | I                      | EVDD           | _                                  | AA18                                                       |  |  |

| FEC1_RXCLK    | PFEC1H3     | _                     | ATA_DATA5      | _                                         | I                      | EVDD           | _                                  | W14                                                        |  |  |

| FEC1_RXDV     | PFEC1H2     | FEC1_RMII_<br>CRS_DV  | ATA_DATA15     | _                                         | I                      | EVDD           | _                                  | AB15                                                       |  |  |

| FEC1_RXD[3:2] | PFEC1L[3:2] | _                     | ATA_DATA[4:3]  | _                                         | I                      | EVDD           | _                                  | AA15, Y15                                                  |  |  |

| FEC1_RXD1     | PFEC1L1     | FEC1_RMII_RXD1        | ATA_DATA14     | _                                         | I                      | EVDD           | _                                  | AA17                                                       |  |  |

| FEC1_RXD0     | PFEC1H1     | FEC1_RMII_RXD0        | ATA_DATA13     | _                                         | I                      | EVDD           | _                                  | Y17                                                        |  |  |

| FEC1_RXER     | PFEC1L0     | FEC1_RMII_RXER        | ATA_DATA12     | _                                         | I                      | EVDD           | _                                  | W17                                                        |  |  |

| FEC1_TXCLK    | PFEC1H7     | FEC1_RMII_<br>REF_CLK | ATA_DATA11     | _                                         | 1                      | EVDD           | _                                  | AB19                                                       |  |  |

| FEC1_TXD[3:2] | PFEC1L[7:6] | _                     | ATA_DATA[2:1]  | _                                         | 0                      | EVDD           | _                                  | Y19, W18                                                   |  |  |

| FEC1_TXD1     | PFEC1L5     | FEC1_RMII_TXD1        | ATA_DATA10     | _                                         | 0                      | EVDD           | _                                  | AA19                                                       |  |  |

| FEC1_TXD0     | PFEC1H5     | FEC1_RMII_TXD0        | ATA_DATA9      | _                                         | 0                      | EVDD           | _                                  | Y20                                                        |  |  |

| FEC1_TXEN     | PFEC1H6     | FEC1_RMII_TXEN        | ATA_DATA8      | _                                         | 0                      | EVDD           | _                                  | AA21                                                       |  |  |

| FEC1_TXER     | PFEC1L4     | _                     | ATA_DATA0      | _                                         | 0                      | EVDD           | _                                  | AA22                                                       |  |  |

|               |             | US                    | BB On-the-Go   |                                           | · I                    | •              |                                    |                                                            |  |  |

| USB_DM        | _           | _                     | _              | _                                         | 0                      | USB<br>VDD     | F16                                | A14                                                        |  |  |

| USB_DP        | _           | _                     | _              | _                                         | 0                      | USB<br>VDD     | E16                                | A15                                                        |  |  |

| USB_VBUS_EN   | PUSB1       | USB_PULLUP            | ULPI_NXT       | _                                         | 0                      | USB<br>VDD     | E5                                 | AA2                                                        |  |  |

| USB_VBUS_OC   | PUSB0       | _                     | ULPI_STP       | UD <sup>7</sup>                           | I                      | USB<br>VDD     | В3                                 | V4                                                         |  |  |

MCF5445x ColdFire® Microprocessor Data Sheet, Rev. 9, 04/2021

Table 4. MCF5445x Signal Information and Muxing (continued)

| Signal Name      | GPIO       | Alternate 1   | Alternate 2        | Pull-up (U) <sup>1</sup><br>Pull-down (D) | Direction <sup>2</sup> | Voltage Domain | MCF54450<br>MCF54451<br>256 MAPBGA | MCF54452<br>MCF54453<br>MCF54454<br>MCF54455<br>360 TEPBGA |  |  |  |

|------------------|------------|---------------|--------------------|-------------------------------------------|------------------------|----------------|------------------------------------|------------------------------------------------------------|--|--|--|

|                  |            |               | ATA                |                                           |                        |                |                                    |                                                            |  |  |  |

| ATA_BUFFER_EN    | PATAH5     | _             | _                  | _                                         | 0                      | EVDD           | _                                  | Y13                                                        |  |  |  |

| ATA_CS[1:0]      | PATAH[4:3] | _             | _                  | _                                         | 0                      | EVDD           | _                                  | W21, W22                                                   |  |  |  |

| ATA_DA[2:0]      | PATAH[2:0] | _             | _                  | _                                         | 0                      | EVDD           | _                                  | V19–21                                                     |  |  |  |

| ATA_RESET        | PATAL2     | _             | _                  | _                                         | 0                      | EVDD           | _                                  | W13                                                        |  |  |  |

| ATA_DMARQ        | PATAL1     | _             | _                  | _                                         | I                      | EVDD           | _                                  | AA14                                                       |  |  |  |

| ATA_IORDY        | PATAL0     | _             | _                  | _                                         | -1                     | EVDD           | _                                  | Y14                                                        |  |  |  |

|                  |            | Re            | al Time Clock      | •                                         |                        | •              |                                    |                                                            |  |  |  |

| EXTAL32K         | _          | _             | _                  | _                                         | -1                     | EVDD           | J16                                | A13                                                        |  |  |  |

| XTAL32K          | _          | <del>_</del>  | _                  | _                                         | 0                      | EVDD           | H16                                | A12                                                        |  |  |  |

|                  | SSI        |               |                    |                                           |                        |                |                                    |                                                            |  |  |  |

| SSI_MCLK         | PSSI4      |               | _                  | _                                         | 0                      | EVDD           | T13                                | D20                                                        |  |  |  |

| SSI_BCLK         | PSSI3      | U1CTS         | _                  | _                                         | I/O                    | EVDD           | R13                                | E19                                                        |  |  |  |

| SSI_FS           | PSSI2      | U1RTS         | _                  | _                                         | I/O                    | EVDD           | P12                                | E20                                                        |  |  |  |

| SSI_RXD          | PSSI1      | U1RXD         | _                  | UD                                        | I                      | EVDD           | T12                                | D21                                                        |  |  |  |

| SSI_TXD          | PSSI0      | U1TXD         | _                  | UD                                        | 0                      | EVDD           | R12                                | D22                                                        |  |  |  |

|                  |            |               | I <sup>2</sup> C   |                                           |                        | l .            |                                    |                                                            |  |  |  |

| I2C_SCL          | PFECI2C1   | <u> </u>      | U2TXD              | U                                         | I/O                    | EVDD           | КЗ                                 | AA12                                                       |  |  |  |

| I2C_SDA          | PFECI2C0   |               | U2RXD              | U                                         | I/O                    | EVDD           | K4                                 | Y12                                                        |  |  |  |

|                  |            |               | DMA                |                                           |                        |                |                                    |                                                            |  |  |  |

| DACK1            | PDMA3      |               | _                  |                                           | 0                      | EVDD           | M14                                | C17                                                        |  |  |  |

| DREQ1            | PDMA2      |               | ULPI_DIR USB_CLKIN | U                                         | ı                      | EVDD           | P16                                | C18                                                        |  |  |  |

| DACK0            | PDMA1      | DSPI_PCS3     | OOD_OLINIA         |                                           | 0                      | EVDD           | N15                                | A18                                                        |  |  |  |

| DREQ0            | PDMA0      |               |                    | U                                         | 1                      | EVDD           | N16                                | B18                                                        |  |  |  |

| DIVERSO          | I DIVIAU   | - <del></del> | DSPI               |                                           |                        |                | 0                                  | 210                                                        |  |  |  |

| DOD! DOOS (DOOS) | DD ODIO    |               |                    | 1                                         |                        | 5) (0.0        |                                    |                                                            |  |  |  |

| DSPI_PCS5/PCSS   | PDSPI6     |               | _                  | _                                         | 0                      | EVDD           | N14                                | D18                                                        |  |  |  |

| DSPI_PCS2        | PDSPI5     |               | _                  | _                                         | 0                      | EVDD           | L13                                | A19                                                        |  |  |  |

| DSPI_PCS1        | PDSPI4     | SBF_CS        | _                  | <u> </u>                                  | 0                      | EVDD           | P14                                | B20                                                        |  |  |  |

| DSPI_PCS0/SS     | PDSPI3     |               | _                  | U                                         | I/O                    | EVDD           | R16                                | D17                                                        |  |  |  |

| DSPI_SCK         | PDSPI2     | SBF_CK        | _                  | _                                         | I/O                    | EVDD           | R15                                | A20                                                        |  |  |  |

Table 4. MCF5445x Signal Information and Muxing (continued)

| Signal Name  DSPI_SIN | <b>GPIO</b> PDSPI1                                                                 | Alternate 1  SBF_DI | Alternate 2           | Pull-up (U) <sup>1</sup> Pull-down (D) | – Direction <sup>2</sup> | Voltage Domain | MCF54450<br>MCF54451<br>256 MAPBGA | MCF54452<br>MCF54453<br>MCF54454<br>MCF54455<br>360 TEPBGA |  |  |  |

|-----------------------|------------------------------------------------------------------------------------|---------------------|-----------------------|----------------------------------------|--------------------------|----------------|------------------------------------|------------------------------------------------------------|--|--|--|

|                       |                                                                                    |                     | _                     |                                        | 0                        | EVDD           |                                    |                                                            |  |  |  |

| DSPI_SOUT             | PDSPI0                                                                             | SBF_DO              | _                     | _                                      | U                        | EVDD           | N13                                | C20                                                        |  |  |  |

|                       |                                                                                    |                     | UARTs                 |                                        |                          |                |                                    |                                                            |  |  |  |

| U1CTS                 | PUART7                                                                             | _                   | _                     | _                                      | I                        | EVDD           | _                                  | V3                                                         |  |  |  |

| U1RTS                 | PUART6                                                                             | _                   | _                     | _                                      | 0                        | EVDD           | _                                  | U4                                                         |  |  |  |

| U1RXD                 | PUART5                                                                             | _                   | _                     | _                                      | I                        | EVDD           | _                                  | P3                                                         |  |  |  |

| U1TXD                 | PUART4                                                                             | _                   | _                     | _                                      | 0                        | EVDD           | _                                  | N3                                                         |  |  |  |

| U0CTS                 | PUART3                                                                             | _                   | _                     | _                                      | I                        | EVDD           | M3                                 | Y16                                                        |  |  |  |

| U0RTS                 | PUART2                                                                             | _                   | _                     | _                                      | 0                        | EVDD           | M2                                 | AA16                                                       |  |  |  |

| U0RXD                 | PUART1                                                                             | _                   | _                     | _                                      | I                        | EVDD           | N1                                 | AB16                                                       |  |  |  |

| U0TXD                 | PUART0                                                                             | _                   | _                     | _                                      | 0                        | EVDD           | M1                                 | W15                                                        |  |  |  |

| Note: The UART1 and   | Note: The UART1 and UART 2 signals are multiplexed on the DMA timers and I2C pins. |                     |                       |                                        |                          |                |                                    |                                                            |  |  |  |

|                       |                                                                                    | Ι                   | OMA Timers            |                                        |                          |                |                                    |                                                            |  |  |  |

| DT3IN                 | PTIMER3                                                                            | DT3OUT              | U2RXD                 | _                                      | I                        | EVDD           | C13                                | H2                                                         |  |  |  |

| DT2IN                 | PTIMER2                                                                            | DT2OUT              | U2TXD                 | _                                      | I                        | EVDD           | D13                                | H1                                                         |  |  |  |

| DT1IN                 | PTIMER1                                                                            | DT1OUT              | U2CTS                 | _                                      | I                        | EVDD           | B14                                | H3                                                         |  |  |  |

| DT0IN                 | PTIMER0                                                                            | DT0OUT              | U2RTS                 | _                                      | I                        | EVDD           | A15                                | G1                                                         |  |  |  |

| -                     |                                                                                    | i                   | BDM/JTAG <sup>9</sup> | l                                      |                          | I              | I                                  |                                                            |  |  |  |

| PSTDDATA[7:0]         | _                                                                                  | _                   | _                     | _                                      | 0                        | EVDD           | E2, D1, F4, E3, D2,<br>C1, E4, D3  | AA6, AB6, AB5,<br>W6, Y6, AA5, AB4,<br>Y5                  |  |  |  |

| JTAG_EN               | _                                                                                  | _                   | _                     | D                                      | I                        | EVDD           | M11                                | C21                                                        |  |  |  |

| PSTCLK                | _                                                                                  | TCLK                | _                     | _                                      | I                        | EVDD           | P13                                | C22                                                        |  |  |  |

| DSI                   | _                                                                                  | TDI                 | _                     | U                                      | I                        | EVDD           | T15                                | C19                                                        |  |  |  |

| DSO                   | _                                                                                  | TDO                 | _                     | _                                      | 0                        | EVDD           | T14                                | A21                                                        |  |  |  |

| BKPT                  | _                                                                                  | TMS                 | _                     | U                                      | I                        | EVDD           | R14                                | B21                                                        |  |  |  |

| DSCLK                 | _                                                                                  | TRST                | _                     | U                                      | I                        | EVDD           | M13                                | B22                                                        |  |  |  |

|                       |                                                                                    |                     | Test                  |                                        |                          |                | I                                  | 1                                                          |  |  |  |

| TEST                  | _                                                                                  | _                   | _                     | D                                      | I                        | EVDD           | M6                                 | AB20                                                       |  |  |  |

| PLLTEST               | _                                                                                  |                     | _                     | _                                      | 0                        | EVDD           | K16                                | D15                                                        |  |  |  |

Table 4. MCF5445x Signal Information and Muxing (continued)

| Signal Name | GPIO | Alternate 1 | Alternate 2  | Pull-up (U) <sup>1</sup><br>Pull-down (D) | Direction <sup>2</sup> | Voltage Domain | MCF54450<br>MCF54451<br>256 MAPBGA                         | MCF54452<br>MCF54453<br>MCF54454<br>MCF54455<br>360 TEPBGA                                                                                                                           |

|-------------|------|-------------|--------------|-------------------------------------------|------------------------|----------------|------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             |      | Ро          | wer Supplies |                                           |                        |                |                                                            |                                                                                                                                                                                      |

| IVDD        | _    | _           | _            | _                                         | _                      | _              | E6–12, F5, F12                                             | D6, D8, D14, F4,<br>H4, N4, R4, W4,<br>W7, W8, W12,<br>W16, W19                                                                                                                      |

| EVDD        | _    | _           | _            | _                                         | _                      | _              | G5, G12, H5, H12,<br>J5, J12, K5, K12,<br>L5–6, L12        | D13, D19, G8,<br>G11, G14, G16, J7,<br>J16, L7, L16, N16,<br>P7, R16, T8, T12,<br>T14, T16                                                                                           |

| SD_VDD      | _    | _           | _            | _                                         | _                      | _              | L7-11, M9, M10                                             | F19, H19, K19,<br>M19, R19, U19                                                                                                                                                      |

| VDD_OSC     | _    | _           | _            | _                                         | _                      | _              | L14                                                        | B16                                                                                                                                                                                  |

| VDD_A_PLL   | _    | _           | _            | _                                         | _                      | _              | K15                                                        | C14                                                                                                                                                                                  |

| VDD_RTC     | _    | _           | _            | _                                         | _                      | _              | M12                                                        | C13                                                                                                                                                                                  |

| VSS         | _    | _           | _            | _                                         | _                      | _              | A1, A16, F6–11,<br>G6–11, H6–11, J6–<br>11, K6–11, T1, T16 | A1, A22, B14, G7,<br>G9–10, G12–13,<br>G15, H7, H16, J9–<br>14, K7, K9–14,<br>K16, L9–14, M7,<br>M9–M14, M16, N7,<br>N9–14, P9–14,<br>P16, R7, T7, T9–<br>11, T13, T15, AB1,<br>AB22 |

| VSS_OSC     | _    |             |              | _                                         |                        |                | L15                                                        | C16                                                                                                                                                                                  |

Pull-ups are generally only enabled on pins with their primary function, except as noted.

For the 360 TEPBGA, booting with PCI disabled results in all dedicated PCI pins being safe-stated. The PCI\_GNT and PCI\_REQ lines and IRQ1/PCI\_INTA come up as GPIO.

<sup>&</sup>lt;sup>2</sup> Refers to pin's primary function.

<sup>&</sup>lt;sup>3</sup> Enabled only in oscillator bypass mode (internal crystal oscillator is disabled).

<sup>&</sup>lt;sup>4</sup> Serial boot must select 0-bit boot port size to enable the GPIO mode on these pins.

When the PCI is enabled, all PCI bus pins come up configured as such. This includes the PCI\_GNT and PCI\_REQ lines, which have GPIO. The IRQ1/PCI\_INTA signal is a special case. It comes up as PCI\_INTA when booting as a PCI agent and as GPIO when booting as a PCI host.

<sup>&</sup>lt;sup>6</sup> GPIO functionality is determined by the edge port module. The pin multiplexing and control module is only responsible for assigning the alternate functions.

Depends on programmed polarity of the USB\_VBUS\_OC signal.

<sup>&</sup>lt;sup>8</sup> Pull-up when the serial boot facility (SBF) controls the pin

<sup>&</sup>lt;sup>9</sup> If JTAG\_EN is asserted, these pins default to Alternate 1 (JTAG) functionality. The pin multiplexing and control module is not responsible for assigning these pins.

#### 4.2 Pinout—256 MAPBGA

The pinout for the MCF54450 and MCF54451 packages are shown below.

|   | 1              | 2             | 3                   | 4              | 5                   | 6          | 7            | 8           | 9           | 10          | 11          | 12          | 13            | 14            | 15            | 16            |   |

|---|----------------|---------------|---------------------|----------------|---------------------|------------|--------------|-------------|-------------|-------------|-------------|-------------|---------------|---------------|---------------|---------------|---|

| A | VSS            | FB_OE         | FB_TS               | FB_BE/<br>BWE0 | FB_BE/<br>BWE2      | FB_AD<br>2 | FB_AD<br>6   | FB_AD<br>10 | FB_AD<br>14 | FB_AD<br>18 | FB_AD<br>22 | FB_AD<br>26 | FB_AD<br>30   | FB_AD<br>31   | TOIN          | VSS           | Α |

| В | FB_TA          | FB_R/W        | USB_<br>VBUS_<br>OC | FB_BE/<br>BWE1 | FB_BE/<br>BWE3      | FB_AD      | FB_AD<br>7   | FB_AD<br>11 | FB_AD<br>15 | FB_AD<br>19 | FB_AD<br>23 | FB_AD<br>27 | FB_CLK        | T1IN          | FB_A<br>4     | FB_A<br>6     | В |

| С | PST<br>DDATA2  | FB_CS3        | FB_CS1              | FB_CS0         | FB_AD<br>0          | FB_AD<br>4 | FB_AD<br>8   | FB_AD<br>12 | FB_AD<br>16 | FB_AD<br>20 | FB_AD<br>24 | FB_AD<br>28 | T3IN          | FB_A<br>3     | FB_A<br>5     | FB_A<br>1     | С |

| D | PST<br>DDATA6  | PST<br>DDATA3 | PST<br>DDATA0       | FB_CS2         | FB_AD<br>1          | FB_AD<br>5 | FB_AD<br>9   | FB_AD<br>13 | FB_AD<br>17 | FB_AD<br>21 | FB_AD<br>25 | FB_AD<br>29 | T2IN          | FB_A<br>0     | FB_A<br>2     | FB_A<br>7     | D |

| E | FEC0_<br>COL   | PST<br>DDATA7 | PST<br>DDATA4       | PST<br>DDATA1  | USB_<br>VBUS_<br>EN | IVDD       | IVDD         | IVDD        | IVDD        | IVDD        | IVDD        | IVDD        | FB_A<br>8     | FB_A<br>9     | FB_A<br>10    | USB_<br>DP    | E |

| F | FEC0_<br>CRS   | FEC0_<br>MDIO | FEC0_<br>MDC        | PST<br>DDATA5  | IVDD                | VSS        | VSS          | VSS         | VSS         | VSS         | VSS         | IVDD        | FB_A<br>11    | FB_A<br>12    | IRQ_1         | USB_<br>DM    | F |

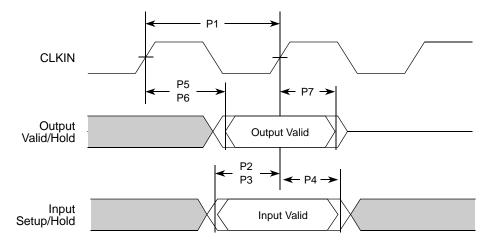

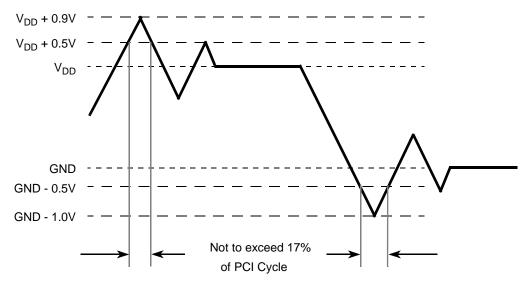

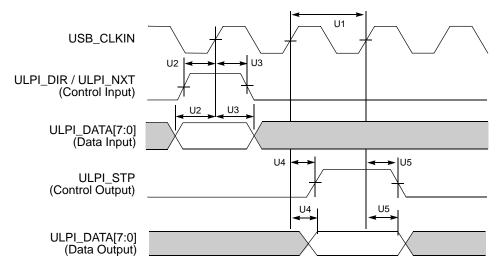

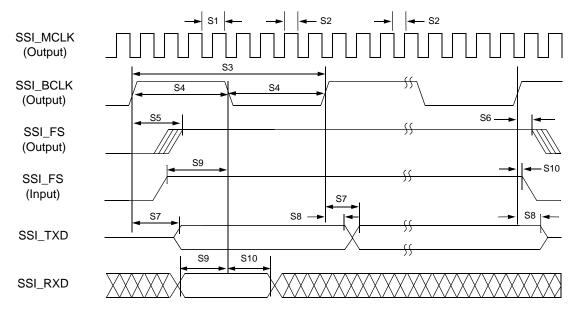

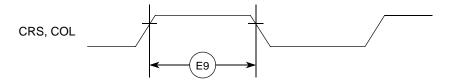

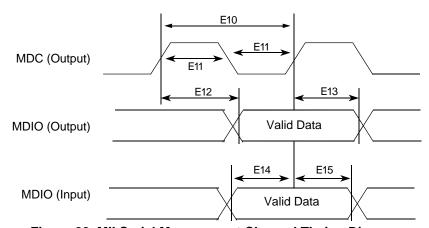

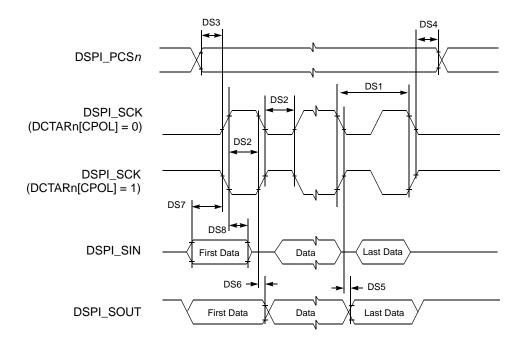

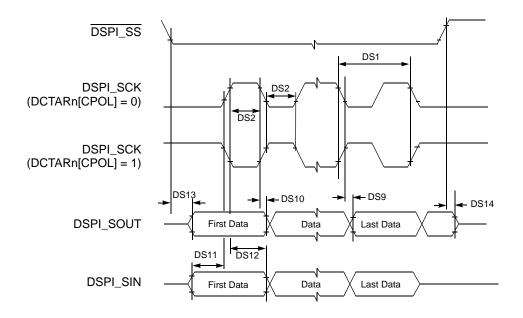

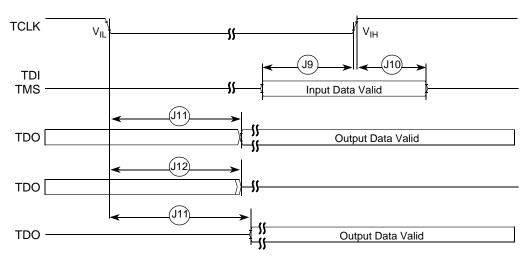

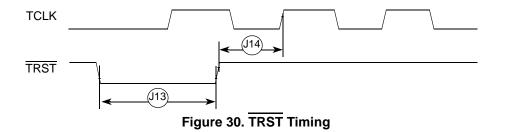

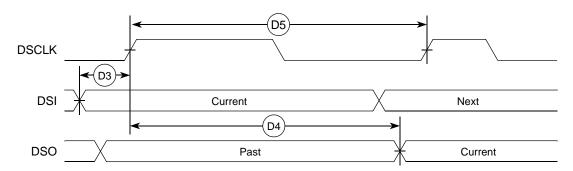

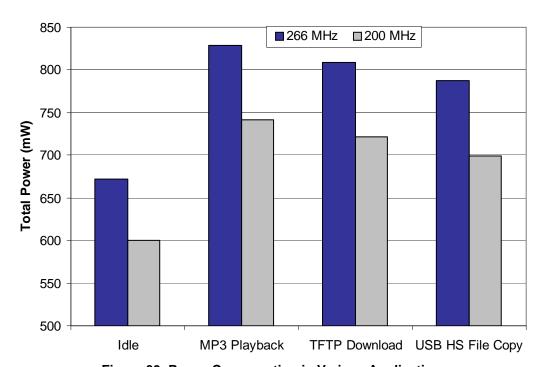

| G | FEC0_<br>RXCLK | FEC0_<br>RXDV | FEC0_<br>RXD3       | FEC0_<br>RXD2  | EVDD                | VSS        | VSS          | VSS         | VSS         | VSS         | VSS         | EVDD        | FB_A<br>13    | FB_A<br>14    | FB_A<br>15    | NC            | G |