# Current Mode PWM Controller with Synchronous Secondary Gate Drive

## The Future of Analog IC Technology

### **DESCRIPTION**

The MP3908 is a flexible current-mode PWM controller optimized for power-supply The MP3908 features resistorapplications. programmable dead-time control to optimize efficiency for a broad number of different configurations, and a synchronous secondary gate drive. The MOSFET drivers are capable of driving >10A MOSFETs. It has an operational current of typically 270µA and can accommodate off-line. Telecom and non-isolated applications. Under-voltage lockout. soft-start. slope compensation and peak current limiting are all included. In a boost application, with an output voltage of less than 28V, the current sense pin can connect directly to the drain of the external switch. This eliminates the requirement for an additional current sensing element and its associated efficiency loss.

While designed for boost applications, the MP3908 can also be used for other topologies including Forward, Flyback and Sepic. The 10V gate driver compliance minimizes the power loss of the external MOSFET while allowing the use of a wide variety of standard threshold devices. An externally programmable delay following the turn off of the synchronous rectifier allows the incorporation of secondary side synchronous rectifier

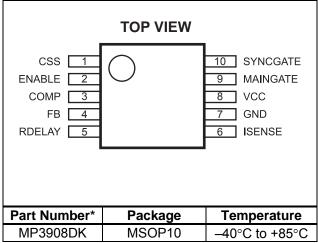

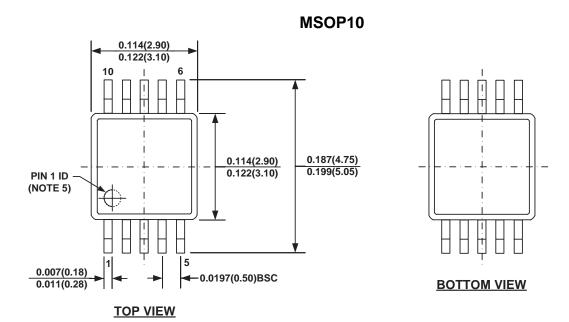

The MP3908 is available in space saving 10-pin MSOP package.

### **FEATURES**

- Programmable Dead-Time

- Synchronous Secondary Gate Drive

- Current Mode Control

- 10V MOSFET Gate Drivers

- Drives >10A MOSFETs

- Soft-Start

- Cycle-by-Cycle Current Limiting

- Slope Current Compensation

- Lossless Current Sense (V<sub>ISENSE</sub><28V)</li>

- 50µA Shutdown Current

- 270uA typical Operating Current

- 250KHz Constant Frequency Operation

- Applicable to Boost, SEPIC, Flyback and Forward Topologies

- Available in a 10-Pin MSOP Package

### **APPLICATIONS**

- PoE PD Power Supplies

- TV CCFL Power Generation

- Telecom Isolated Power

- Brick Modules

- Off-line Controller

"MPS" and "The Future of Analog IC Technology" are Registered Trademarks of Monolithic Power Systems, Inc.

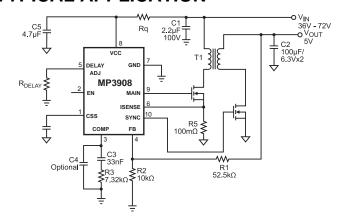

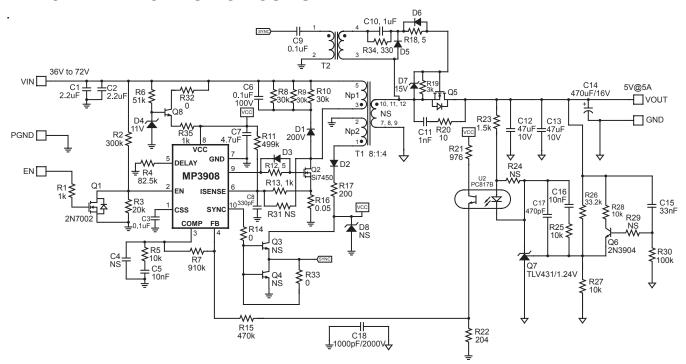

### TYPICAL APPLICATION

### PACKAGE REFERENCE

For Tape & Reel, add suffix –Z (eg. MP3908DK–Z)

For RoHS compliant packaging, add suffix –LF (eg. MP3908DK–LF–Z)

## ABSOLUTE MAXIMUM RATINGS (1)

| VCC<br>VCC Maximum Current |                    |

|----------------------------|--------------------|

| ISENSE                     |                    |

| FB                         | 0.3V to +1.3V      |

| COMP                       | 0.3V to +3V        |

| CSS, ENABLE                | 0.3V to +5V        |

| Junction Temperature       |                    |

| Lead Temperature           | 260°C              |

| Storage Temperature        | –65°C to +150°C    |

| Recommended Operat         | ing Conditions (2) |

###

| Thermal Resistance (3) | $oldsymbol{	heta}_{JA}$ | $	heta_{JC}$ |      |

|------------------------|-------------------------|--------------|------|

| MSOP10                 | . 150                   | 65           | °C/W |

#### Notes:

- 1) Exceeding these ratings may damage the device.

- The device is not guaranteed to function outside of its operating conditions.

- 3) Measured on approximately 1" square of 1 oz copper.

### **ELECTRICAL CHARACTERISTICS**

$V_{CC} = 10V$ ,  $T_A = +25$ °C, unless otherwise noted.

| Parameter                                       | Symbol          | Condition                                                                    | Min   | Тур   | Max   | Units |

|-------------------------------------------------|-----------------|------------------------------------------------------------------------------|-------|-------|-------|-------|

| VCC Undervoltage Lockout                        |                 | Internal Divider (I <sub>Q</sub> )                                           |       | 4.5   | 4.7   | V     |

| VCC On/Off Voltage Hysteresis                   |                 |                                                                              |       | 1     |       | V     |

| Shutdown Current                                | Is              | EN/SS = 0V, V <sub>IN</sub> = 9V                                             |       | 50    |       | μA    |

| Quiescent Current (Operation)                   | IQ              | Output not switching, V <sub>FB</sub> = 1V, V <sub>CC</sub> = 9V             |       | 270   | 320   | μΑ    |

| Main Gate Driver Impedance (Sourcing)           |                 | V <sub>CC</sub> = 9V, V <sub>GATE</sub> = 5V                                 |       | 16    |       | Ω     |

| Main Gate Driver Impedance (Sinking)            |                 | V <sub>CC</sub> = 9V, I <sub>GATE</sub> = 5mA                                |       | 5.0   |       | Ω     |

| Synchronous Gate Driver<br>Impedance (Sourcing) |                 | V <sub>CC</sub> = 9V, V <sub>SYNCGATE</sub> = 5V                             |       | 16    |       | Ω     |

| Synchronous Gate Driver Impedance (Sinking)     |                 | $V_{CC}$ = 9V, $I_{GATE}$ = 5mA                                              |       | 5.0   |       | Ω     |

| Delay after Synchronous Gate                    |                 | $R_{DELAY}$ =100k $\Omega$                                                   |       | 50    |       | ns    |

| Error Amplifier Transconductance                |                 | $V_{FB}$ connected to $V_{COMP/RUN}$ . Force ±10 $\mu$ A to $V_{COMP/RUN}$ . | 0.26  | 0.38  | 0.46  | mA/V  |

| Maximum Comp Current                            |                 | Sourcing and Sinking                                                         |       | 40    |       | μΑ    |

| Error Amplifier Translator Gain (4)             | $A_{ET}$        |                                                                              | 0.28  | 0.32  | 0.36  | V/V   |

| Switching Frequency                             | $f_{S}$         |                                                                              | 220   | 260   | 300   | KHz   |

| Thermal Shutdown                                |                 |                                                                              |       | 150   |       | °C    |

| Maximum Duty Cycle                              |                 |                                                                              | 76    | 81    | 86    | %     |

| Minimum On Time                                 | t <sub>ON</sub> |                                                                              |       | 200   |       | ns    |

| ISENSE Limit                                    |                 |                                                                              | 165   | 190   | 215   | mV    |

| FB Voltage                                      | $V_{FB}$        |                                                                              | 0.794 | 0.818 | 0.847 | V     |

| FB Bias Current                                 | I <sub>FB</sub> | Current flowing out of part                                                  |       | 50    |       | nA    |

#### Note:

4) Guaranteed by design.

## **ELECTRICAL CHARACTERISTICS** (continued)

$V_{CC} = 10V$ ,  $T_A = +25$ °C, unless otherwise noted.

| Parameter           | Symbol             | Condition                   | Min  | Тур  | Max  | Units |

|---------------------|--------------------|-----------------------------|------|------|------|-------|

| ISENSE Bias Current | I <sub>SENSE</sub> | Current flowing out of part |      | 50   |      | nA    |

| Enable On Threshold | $V_{EN}$           | High-to-Low                 | 1.15 | 1.25 | 1.35 | V     |

| Enable Hysteresis   | $V_{EN}$           |                             |      | 50   |      | mV    |

| Soft Start Current  | I <sub>SS</sub>    |                             |      | 4    |      | μA    |

### **PIN FUNCTIONS**

| Pin# | Name      | Description                                                                                                                                                                                                                                                                                                                             |

|------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | CSS       | Capacitor Soft Start. A charging current of 5µA is enabled when the ENABLE pin is taken above 1.2V. The rise time of the capacitor allows output current soft start. Full output current is allowed when the voltage is above 2.7V.                                                                                                     |

| 2    | ENABLE    | This pin serves two functions. Below 0.6V, the part is in sleep mood, drawing 10µA (typ). The second threshold of 1.2V can be used as a precise under-voltage lock out (UVLO) and enables full operation                                                                                                                                |

| 3    | COMP      | Compensation.                                                                                                                                                                                                                                                                                                                           |

| 4    | FB        | Feedback forces this pin voltage to the 0.8V internal reference potential. Do not allow this pin to rise above 1.2V in the application.                                                                                                                                                                                                 |

| 5    | RDELAY    | External resistor determines delay between the Synchronous Gate Drive pin going low to the Main Gate drive going high.                                                                                                                                                                                                                  |

| 6    | ISENSE    | Current Sense. Do not connect this pin directly to the drain of the external MOSFET if the voltage swing exceeds 27V in the particular application. During normal operation, this pin will sense the voltage across the external MOSFET or sense resistor if one is used, limiting the peak inductor current on a cycle-by-cycle basis. |

| 7    | GND       | Ground.                                                                                                                                                                                                                                                                                                                                 |

| 8    | VCC       | Input Supply. Decouple this pin as close as possible to the GND pin.                                                                                                                                                                                                                                                                    |

| 9    | MAIN GATE | This pin drives the external MAIN MOSFET device.                                                                                                                                                                                                                                                                                        |

| 10   | SYNC GATE | This pin drives the external SYNCHRONOUS MOSFET device. The Sync Gate is disabled at the end of switching period if Main Gate is not turned on the next cycle.                                                                                                                                                                          |

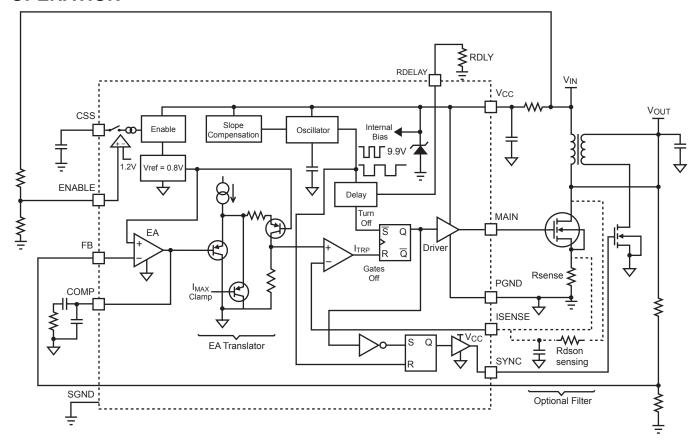

### **OPERATION**

Figure 1—Functional Block Diagram

The MP3908 uses a constant frequency, peak current mode architecture to regulate the feedback voltage. The operation of the MP3908 can be understood with the block diagram of Figure 1.

At the beginning of each cycle the main external N-Channel MOSFET is turned on, forcing the current in the inductor to increase. The current through the FET can either be sensed through a sensing resistor or across the external FET directly. This voltage is then compared to a voltage related to the COMP/RUN node voltage. The voltage at the COMP/RUN pin is an amplified voltage of the difference between the 0.8V reference and the feedback node voltage.

When the voltage at the ISENSE node rises above the voltage set by the COMP/RUN pin, the external main FET is turned off and the synchronous FET, if used, is turned on. The inductor current then flows to the output capacitor through the Schottky diode. The inductor current is controlled by the COMP/RUN voltage, which itself is controlled by the output voltage. The peak inductor current is internally limited by the  $I_{MAX}$  clamp voltage that limits the voltage applied to the  $I_{TRP}$  comparator input.

Thus the output voltage controls the inductor current to satisfy the load. This current mode architecture improves transient response and control loop stability over a voltage mode architecture.

## APPLICATION INFORMATION COMPONENT SELECTION

### **Setting the Output Voltage**

Set the output voltage by selecting the resistive voltage divider ratio. If we use  $10k\Omega$  for the low-side resistor (R2) of the voltage divider, we can determine the high-side resistor (R1) by the equation:

$$R1 = \frac{R2 \times (V_{OUT} - V_{REF})}{V_{REF}}$$

Where  $V_{OUT}$  is the output voltage.

For R2=10k $\Omega$ , V<sub>OUT</sub>=25V and V<sub>REF</sub>=0.8V, then R1=301k $\Omega$ .

An external resistor tied from the R<sub>DELAY</sub> pin to ground programs an internal time delay circuit that sets a delay from the turn off of the synchronous MOSFET drive pin output to the turn on of the main MOSFET drive pin output. This delay is adjustable to program the required time interval required by the circuitry to turn off the synchronous MOSFET from the time that the Synchronous output drive signal goes low. This path may include active devices as well as an isolating transformer used to electrically isolate the secondary side output. Efficiency losses can be quite significant if an overlap occurs between the main and synchronous switching MOSFETs if the delay is not carefully determined and accounted for. The R<sub>DELAY</sub> pin has an internal resistance of approximately 50kOhms that should be added to any external resistance used to approximate the delay interval. Shorting the pin directly to ground will result in approximately 30nSec delay as a result of this internal resistance. A graph is provided in the applications section of this data sheet to illustrate the typical delay time generated versus the resistor value selected

## **Selecting the Inductor and Current Sensing Resistor**

The inductor is required to transfer the energy between the input source and the output capacitors. A larger value inductor results in less ripple current that results in lower peak inductor current, and therefore reduces the stress on the power MOSFET. However, the larger value inductor has a larger physical size, higher series resistance, and/or lower saturation current.

A good rule of thumb is to allow the peak-to-peak ripple current to be approximately 30-50% of the maximum input current. Make sure that the peak inductor current is below 80% of the IC's maximum current limit at the operating duty cycle to prevent loss of regulation. Make sure that the inductor does not saturate under the worst-case load transient and startup conditions. The required inductance value can be calculated by:

$$L = \frac{V_{IN(MIN)} \times (V_{OUT} - V_{IN(MIN)})}{V_{OUT} \times f_{SW} \times \Delta I}$$

$$I_{IN(MAX)} = \frac{V_{OUT} \times I_{LOAD(MAX)}}{V_{IN(MIN)} \times \eta}$$

$$\Delta I = (30\% - 50\%)I_{IN(MAX)}$$

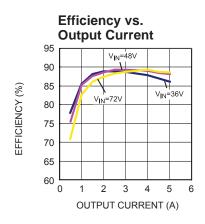

Where  $I_{LOAD\ (MAX)}$  is the maximum load current,  $\Delta I$  is the peak-to-peak inductor ripple current and  $\eta$  is the efficiency. For a typical design, boost converter efficiency can reach 85%~95%.

For  $V_{\text{IN (MIN)}}$ =10V,  $V_{\text{OUT}}$ =25V,  $I_{\text{LOAD (MAX)}}$ =2A, the ripple percentage being 30%,  $\eta$ =95% and  $f_{\text{SW}}$ =330kHz, then L=10 $\mu$ H. In this case, use a 8.8 $\mu$ H inductor (i.e. Sumida CDRH127/LDNP-100MC).

The switch current is usually used for the peak current mode control. In order to avoid hitting the current limit, the voltage across the sensing resistor  $R_{\text{SENSE}}$  should be less than 80% of the worst case current limit voltage, 200mV.

$$R_{\text{SENSE}} = \frac{0.8 \times 0.2}{I_{L(\text{PEAK})}}$$

Where  $I_{L \text{ (PEAK)}}$  is the peak value of the inductor current.

For  $I_{L (PEAK)} = 5.3A$ ,  $R_{SENSE} = 30 m\Omega$ .

In cases where the  $R_{\text{DS(ON)}}$  of the power MOSFET is used as the sensing resistor, be sure that the  $R_{\text{DS(ON)}}$  is lower than the value calculated above,  $30\text{m}\Omega$

Another factor to take into consideration is the temperature coefficient of the MOSFET  $R_{DS(ON)}$ . As the temperature increases, the  $R_{DS(ON)}$  also increases. Device vendors will usually provide an  $R_{DS(ON)}$  vs. temperature curve and the temperature coefficient in the datasheet. Generally, the MOSFET on resistance will double from 25°C to 125°C.

### **Selecting the Input Capacitor**

An input capacitor (C1) is required to supply the AC ripple current to the inductor, while limiting noise at the input source. A low ESR capacitor is required to keep the noise to the IC at a minimum. Ceramic capacitors are preferred, but tantalum or low-ESR electrolytic capacitors may also suffice.

The capacitance can be calculated as:

$$C_1 \approx \frac{\Delta I}{8 \times \Delta V_{IN(RIPPLE)} \times f_{SW}}$$

Where  $\Delta I$  is the peak-to-peak inductor ripple current and  $\Delta V_{IN(RIPPLE)}$  is the input voltage ripple. When using ceramic capacitors, take into account the vendor specified voltage and temperature coefficients for the particular dielectric being used.

For example, 2.2uF capacitance is sufficient to achieve less then 1% input voltage ripple. Meanwhile, it requires an adequate ripple current rating. Use a capacitor with RMS current rating greater than the inductor ripple current (see Selecting the Inductor to determine the inductor ripple current).

In addition, a smaller high quality ceramic  $0.1\mu F \sim 1\mu F$  capacitor may be placed to absorb the high frequency noise. If using this technique, it is recommended that the larger capacitor be a tantalum or electrolytic type.

### **Selecting the Output Capacitor**

Typically, a boost converter has significant output voltage ripple because the current through the output diode is discontinuous. During the diode off state, all of the load current is supplied by the output capacitor.

Low ESR capacitors are preferred to keep the output voltage ripple to a minimum. The characteristics of the output capacitor also affect the stability of the regulation control system. Ceramic, tantalum or low ESR electrolytic capacitors are recommended. In the case of ceramic capacitors, the impedance of the capacitor at the switching frequency is dominated by the capacitance, and so the output voltage ripple is mostly independent of the ESR. The output voltage ripple is estimated to be:

$$V_{RIPPLE} \approx \frac{\left(1 - \frac{V_{IN}}{V_{OUT}}\right) \times I_{LOAD}}{C2 \times f_{SW}}$$

Where  $V_{\text{RIPPLE}}$  is the output ripple voltage,  $V_{\text{IN}}$  and  $V_{\text{OUT}}$  are the DC input and output voltages respectively,  $I_{\text{LOAD}}$  is the load current,  $f_{\text{SW}}$  is the switching frequency and C2 is the output capacitor.

In the case of tantalum or low-ESR electrolytic capacitors, the ESR dominates the impedance at the switching frequency. Therefore, the output ripple is calculated as:

$$V_{RIPPLE(pk\_pk)} \approx \frac{I_{LOAD} \times R_{ESR} \times V_{OUT}}{V_{IN}}$$

where  $R_{\text{ESR}}$  is the equivalent series resistance of the output capacitors.

For the application shown in page 1, use ceramic capacitor as an example. For  $V_{IN(MIN)}=10V$ ,  $V_{OUT}=25V$ ,  $I_{LOAD(MAX)}=2A$ , and V<sub>RIPPLE</sub>=1% of the output voltage, the capacitance C<sub>2</sub>=14.5µF. Please note that the capacitance could ceramic dramatically decrease as the voltage across the capacitor increases. As a result, larger capacitance is recommended. In this example, place four 4.7µF ceramic capacitors in parallel. The voltage rating is also chosen as 50V.

In the meantime, the RMS current rating of the output capacitor needs to be sufficient to handle

the large ripple current. The RMS current is given by:

$$I_{\text{RIPPLE(RMS)}} \approx \sqrt{\left(I_{\text{IN(MAX)}}^2 - 2 \times I_{\text{LOAD}} \times I_{\text{IN(MAX)}}\right) \times \frac{V_{\text{IN}}}{V_{\text{OUT}}} + I_{\text{LOAD}}^2}$$

$$I_{RIPPLE(RMS)} \approx \sqrt{D(1-D) \times I_{INMAX}}^2 < 0.5 \times I_{INMAX}$$

For  $I_{\text{IN(MAX)}}$ =5.3A,  $I_{\text{LOAD}}$ =2A,  $V_{\text{IN}}$ =12V and  $V_{\text{OUT}}$ =25V,  $I_{\text{RIPPLE(RMS)}}$ =2.64A. Make sure that the output capacitor can handle such an RMS current.

In addition, a smaller high quality ceramic  $0.1\mu F\sim 1uF$  capacitor needs to be placed at the output to absorb the high frequency noise during the commutation between the power MOSFET and the output diode. Basically, the high frequency noise is caused by the parasitic inductance of the trace and the parasitic capacitors of devices. The ceramic capacitor should be placed as close as possible to the power MOSFET and output diode in order to minimize the parasitic inductance and maximize the absorption.

### **Selecting the Power MOSFET**

The MP3908 is capable of driving a wide variety of N-Channel power MOSFETS. The critical parameters of selection of a MOSFET are:

- 1. Maximum drain to source voltage, V<sub>DS(MAX)</sub>

- 2. Maximum current, I<sub>D(MAX)</sub>

- 3. On-resistance, R<sub>DS(ON)</sub>

- 4. Gate source charge  $Q_{\text{GS}}$  and gate drain charge  $Q_{\text{GD}}$

- 5. Total gate charge, Q<sub>G</sub>

Ideally, the off-state voltage across the MOSFET is equal to the output voltage. Considering the voltage spike when it turns off,  $V_{DS(MAX)}$  should be greater than 1.5 times of the output voltage.

The maximum current through the power MOSFET happens when the input voltage is minimum and the output power is maximum. The maximum RMS current through the MOSFET is given by

$$I_{RMS(MAX)} = I_{IN(MAX)} \times \sqrt{D_{MAX}}$$

Where:

$$D_{MAX} \approx \frac{V_{OUT} - V_{IN(MIN)}}{V_{OUT}}$$

The current rating of the MOSFET should be greater than 1.5 times  $I_{RMS}$ .

The on resistance of the MOSFET determines the conduction loss, which is given by:

$$P_{cond} = I_{RMS}^2 \times R_{DS(on)} \times k$$

Where k is the temperature coefficient of the MOSFET. If the  $R_{DS(ON)}$  of the MOSFET is used as the current sensing resistor, make sure the voltage drop across the device does not exceed the current limit value of 190mV.

The switching loss is related to  $Q_{\text{GD}}$  and  $Q_{\text{GS1}}$  which determine the commutation time.  $Q_{\text{GS1}}$  is the charge between the threshold voltage and the plateau voltage when a driver charges the gate, which can be read in the chart of  $V_{\text{GS}}$  vs.  $Q_{\text{G}}$  of the MOSFET datasheet.  $Q_{\text{GD}}$  is the charge during the plateau voltage. These two parameters are needed to estimate the turn on and turn off loss.

$$\begin{split} P_{SW} &= \frac{Q_{GS1} \times R_G}{V_{DR} - V_{TH}} \times V_{DS} \times I_{IN} \times f_{SW} \ + \\ &= \frac{Q_{GD} \times R_G}{V_{DR} - V_{PLT}} \times V_{DS} \times I_{IN} \times f_{SW} \end{split}$$

Where  $V_{\text{TH}}$  is the threshold voltage,  $V_{\text{PLT}}$  is the plateau voltage,  $R_{\text{G}}$  is the gate resistance,  $V_{\text{DS}}$  is the drain-source voltage. Please note that the switching loss is the most difficult part in the loss estimation. The formula above provides a simple physical expression. If more accurate estimation is required, the expressions will be much more complex.

For extended knowledge of the power loss estimation, readers should refer to the book "Power MOSFET Theory and Applications" written by Duncan A. Grant and John Gowar.

The total gate charge,  $Q_{\text{G}}$ , is used to calculate the gate drive loss. The expression is

$$P_{DR} = Q_G \times V_{DR} \times f_{SW}$$

where  $V_{DR}$  is the drive voltage.

For the application in page 1, a FDS6630 or equivalent MOSFET is chosen. Read from the datasheet:  $R_{DS(ON)}$ =28m $\Omega$ , k = 0.5,  $Q_{GD}$ =0.9nC,

$Q_{GS1}$ =1nC,  $V_{TH}$ =1.7V,  $V_{PLT}$ =3V and  $Q_{G}$ =5nC @ 10V. The MP3908 has its gate driving resistance of around 20 $\Omega$  at  $V_{DR}$ =10V and  $V_{GATE}$  = 5V.

Based on the loss calculation above, the conduction loss is around 0.629W. The switching loss is around 0.171W, and the gate drive loss is 0.015W.

### **Selecting the Output Diode**

The output rectifier diode supplies current to the inductor when the MOSFET is off. To reduce losses due to diode forward voltage and recovery time, use a Schottky diode. The diode should be rated for a reverse voltage greater than the output voltage used. Considering the voltage spike during the commutation period, the voltage rating of the diode should be set as 1.5 times the output voltage. For high output voltages (150V or above), a Schottky diode might not be practical. A high-speed ultra-fast recovery silicon rectifier is recommended.

Observation of the boost converter circuit shows that the average current through the diode is the average load current, and the peak current through the diode is the peak current through the inductor. The average current rating must be greater than 1.5 times of the maximum load current, and the peak current rating must be greater than the peak inductor current.

For the application in page 1, a Vishay SS16 Schottky diode or equivalent part is chosen.

### **Boost Converter: Compensation Design**

The output of the transconductance error amplifier (COMP) is used to compensate the regulation control system. The system uses two poles and one zero to stabilize the control loop. The poles are  $f_{P1}$ , which is set by the output capacitor (C2) and load resistance and  $f_{P2}$ , which starts from origin. The zero ( $f_{Z1}$ ) is set by the compensation capacitor (C3) and the compensation resistor (R3). These parameters are determined by the equations:

$$f_{P1} = \frac{1}{\pi \times C2 \times R_{LOAD}}$$

$$f_{Z1} = \frac{1}{2 \times \pi \times C3 \times R3}$$

Where R<sub>LOAD</sub> is the load resistance.

The DC mid-band loop gain is:

$$A_{VDC} = \frac{0.5 \times G_{EA} \times V_{IN} \times R_{LOAD} \times V_{REF} \times R3 \times A_{ET}}{{V_{OUT}}^2 \times R_{SENSE}}$$

where  $V_{\text{REF}}$  is the voltage reference, 0.8V.  $A_{\text{ET}}$  is the gain of error amplifier translator and  $G_{\text{EA}}$  is the error amplifier transconductance.

The ESR zero in this example locates at very high frequency. Therefore, it is not taken into design consideration.

There is also a right-half-plane zero ( $f_{RHPZ}$ ) that exists in continuous conduction mode (inductor current does not drop to zero on each cycle) step-up converters. The frequency of the right half plane zero is:

$$f_{RHPZ} = \frac{V_{IN}^2 \times R_{LOAD}}{2 \times \pi \times L \times V_{OUT}^2}$$

The right-half-plane zero increases the gain and reduces the phase simultaneously, which results in smaller phase margin and gain margin. The worst case happens at the condition of minimum input voltage and maximum output power.

In order to achieve system stability,  $f_{z1}$  is placed close to  $f_{P1}$  to cancel the pole. R3 is adjusted to change the voltage gain. Make sure the bandwidth is about 1/10 of the lower one of the ESR zero and the right-half-plane zero.

$$\frac{1}{\pi \times C2 \times R_{LOAD}} = \frac{1}{2 \times \pi \times C3 \times R3}$$

$$R3 = \frac{V_{OUT}^{2} \times 2 \times \pi \times C2 \times f_{c} \times R_{SENSE}}{G_{EA} \times V_{REF} \times V_{IN} \times A_{ET}}$$

Based on these equations, R3 and C3 can be solved.

For the application in page 1,  $f_{p1}$  = 1.35KHz, ESR zero is much higher than the switching frequency and  $f_{RHPZ}$ =45.8KHz. Set  $f_{z1}$  to 3.18KHz and make the crossover frequency 8.5kHz, then R3=5k $\Omega$  and C3=10nF. Choose 5k $\Omega$  and 10nF.

In cases where the ESR zero is in a relatively low frequency region and results in insufficient gain margin, an optional capacitor (C5) (shown in flat page) should be added. Then a pole, formed by C5 and R3, should be placed at the ESR zero to cancel the adverse effect.

$$C5 = \frac{1}{2 \times \pi \times R3 \times f_{\text{ESRz}}}$$

### **Layout Consideration**

High frequency switching regulators require very careful layout for stable operation and low noise. Keep the high current path as short as possible between the MOSFET drain, output diode, output capacitor and GND pin for minimal noise and ringing. The  $V_{\rm CC}$  capacitor must be placed close to the VCC pin for best decoupling. All feedback components must be kept close to the FB pin to prevent noise injection on the FB pin trace. The ground return of the input and output capacitors should be tied closed to the GND pin. See the MP3908 demo board layout for reference.

### **TYPICAL APPLICATION CIRCUITS**

Figure 2—MP3908 Isolated Synchronous Flyback Application

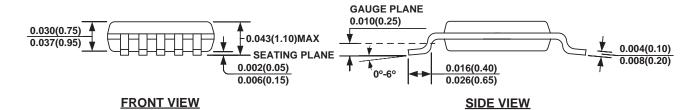

### PACKAGE INFORMATION

### **NOTE:**

- 1) CONTROL DIMENSION IS IN INCHES. DIMENSION IN BRACKET IS IN MILLIMETERS.

- 2) PACKAGE LENGTH DOES NOT INCLUDE MOLD FLASH, PROTRUSION OR GATE BURR.

- 3) PACKAGE WIDTH DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION.

- 4) LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.004" INCHES MAX.

- 5) PIN 1 IDENTIFICATION HAS THE HALF OR FULL CIRCLE OPTION.

- 6) DRAWING MEETS JEDEC MO-817, VARIATION BA.

- 7) DRAWING IS NOT TO SCALE.

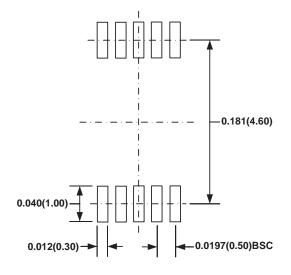

### **RECOMMENDED LAND PATTERN**

**NOTICE:** The information in this document is subject to change without notice. Please contact MPS for current specifications. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.