## $\begin{array}{c} \textbf{NTE5620} \\ \textbf{TRIAC} \\ \textbf{800V}_{\text{RM}}, \, \textbf{8A}, \, \textbf{TO220} \, \, \textbf{Full Pack} \end{array}$

The NTE5620 TRIAC is designed primarily for full-wave AC control applications, such as light dimmers, heater controls, motor controls, and power supplies; or wherever full wave silicon gate controlled solid state devices are needed. TRIAC type thyristors switch from a blocking to a conducting state for either polarity of applied voltage with positive or negative gate triggering.

## Features:

- Blocking Voltage 800 Volts

- All Diffused and Glass Passivated Junctions for Greater Parameter Uniformity and Stability

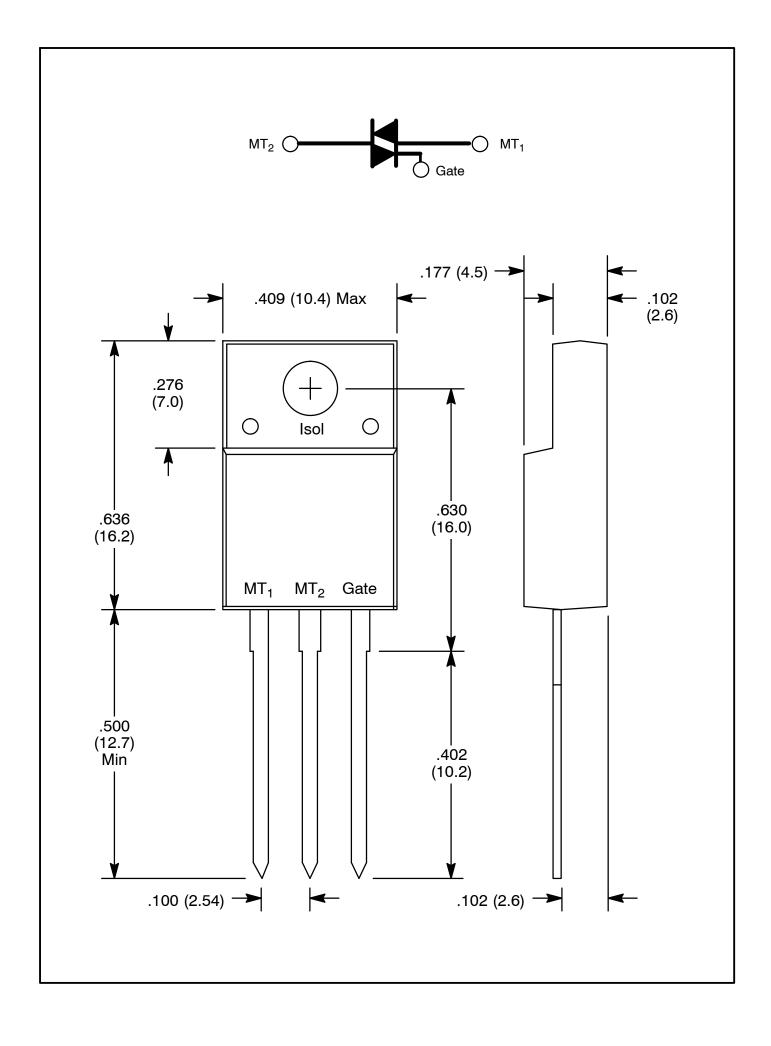

- Small, Rugged, TO220 Full Pack for Low Thermal Resistance, High Heat Dissipation, and Durability

- Gate Triggering Guaranteed in Four Modes

## **Absolute Maximum Ratings:**

| Peak Repetitive Off–State Voltage, $V_{DRM}$ ( $T_J$ = $-40^\circ$ to $+125^\circ$ C, 1/2 Sine Wave 50 to $60H_Z$ , Gate Open, Note 1) 800V |

|---------------------------------------------------------------------------------------------------------------------------------------------|

| On–State Current RMS, $I_{T(RMS)}$ ( $T_C = +80^{\circ}C$ , Full Cycle Sine Wave 50 to $60H_Z$ , Note 2)                                    |

| Peak Non–Repetitive Surge Current, $I_{TSM}$ (One Full Cycle, 60Hz, $T_C$ = +125°C, Preceded and followed by rated current) 100A            |

| Peak Gate Power (T <sub>C</sub> = +80°C, Pulse Width = 2μs), P <sub>GM</sub>                                                                |

| Average Gate Power ( $T_C = +80^{\circ}C$ , $t = 8.3$ ms), $P_{G(AV)}$                                                                      |

| Peak Gate Current (Pulse Width = 2μs), I <sub>GM</sub>                                                                                      |

| RMS Isolation Voltage (T <sub>A</sub> = +25°C, Relative Humidity ≤[20%), V <sub>(ISO)</sub>                                                 |

| Operating Junction Temperature Range, T <sub>J</sub>                                                                                        |

| Storage Temperature Range, T <sub>stg</sub> 40° to +150°C                                                                                   |

| Thermal Resistance, Junction-to-Case, R <sub>thJC</sub>                                                                                     |

| Typical Thermal Resistance, Case-to-Sink, R <sub>thCS</sub>                                                                                 |

| Thermal Resistance, Junction-to-Ambient, R <sub>thJA</sub>                                                                                  |

- Note 1. Ratings apply for open gate conditions. Thyristor devices shall not be tested with a constant current source for blocking capability such that the voltage applied exceeds the rated blocking voltage.

- Note 2. The case temperature reference point for all  $T_C$  measurements is a point on the center lead of the package as close as possible to the plastic body.

## $\underline{\textbf{Electrical Characteristics:}} \text{ (T}_{C} = +25^{\circ}\text{C unless otherwise specified)}$

| Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Symbol           | Min                            | Тур                      | Max                      | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------------------|--------------------------|--------------------------|------|

| Peak Blocking Current (Either Direction) (Rated $V_{DRM}$ , $T_J = +125$ °C, Gate Open)                                                                                                                                                                                                                                                                                                                                                                                                                  | I <sub>DRM</sub> | _                              | -                        | 2                        | mA   |

| Peak On-State Voltage (Either Direction) (I <sub>TM</sub> = 11.3A Peak; Pulse Width = 1 to 2ms, Duty Cycle < 2%)                                                                                                                                                                                                                                                                                                                                                                                         | V <sub>TM</sub>  | _                              | 1.7                      | 2.0                      | V    |

| Peak Gate Trigger Current (Main Terminal Voltage = 12Vdc, R <sub>L</sub> = 100 Ohms) MT2(+), G(+) MT2(+), G(-) MT2(-), G(-) MT2(-), G(+)                                                                                                                                                                                                                                                                                                                                                                 | I <sub>GT</sub>  | 1 1 1                          |                          | 50<br>50<br>50<br>75     | mA   |

| Peak Gate Trigger Voltage $ \begin{array}{l} \text{(Main Terminal Voltage} \\ \text{(Main Terminal Voltage} = 12 \text{Vdc}, \ R_L = 100 \ \text{Ohms}) \\ \text{MT2(+)}, \ G(+) \\ \text{MT2(+)}, \ G(-) \\ \text{MT2(-)}, \ G(-) \\ \text{MT2(-)}, \ G(+) \\ \text{(Main Terminal Voltage} = \text{Rated V}_{DRM}, \ R_L = 10 \text{k}\Omega, \\ \text{T}_J = +125 ^{\circ}\text{C}) \\ \text{MT2(+)}, \ G(+); \ \text{MT2(+)}, \ G(-); \ \text{MT2(-)}, \ G(-) \\ \text{MT2(-)}, \ G(+) \end{array} $ | V <sub>GT</sub>  | -<br>-<br>-<br>-<br>0.2<br>0.2 | 0.9<br>0.9<br>1.1<br>1.4 | 2.0<br>2.0<br>2.0<br>2.5 | V    |

| Holding Current (Either Direction)<br>(Main Terminal Voltage = 24Vdc, Gate Open<br>I <sub>T</sub> = 200mA)                                                                                                                                                                                                                                                                                                                                                                                               | I <sub>H</sub>   | -                              | _                        | 50                       | mA   |

| Critical Rate of Rise of Off–State Voltage (Rated V <sub>DRM</sub> , Exponential Waveform, T <sub>J</sub> = +125°C, Gate Open)                                                                                                                                                                                                                                                                                                                                                                           | dv/dt            | _                              | 100                      | -                        | V/µs |

| Critical Rate of Rise of Commutation Voltage (Rated $V_{DRM}$ , $I_{T(RMS)}$ = 6A, Commutating di/dt = 4.3A/ms, Gate Unenergized, $T_{C}$ = +80°C)                                                                                                                                                                                                                                                                                                                                                       | dv/dt(c)         | П                              | 5                        | _                        | V/µs |